A Peer Reviewed Open Access International Journal

# High Speed Low Power Multiplier using a Vedic Mathematical Approach

Sk.Kaiser M.Tech Student, Department of ECE, KITS for Women's, kodad, T.S, India.

### **ABSTRACT:**

Multiplier design is always a challenging task; how many ever novel designs are proposed, the user needs demands much more optimized ones. Vedic mathematics is world renowned for its algorithms that yield quicker results, be it for mental calculations or hardware design. Power dissipation is drastically reduced by the use of Reversible logic. The reversible Urdhva Tiryakbhayam Vedic multiplier is one such multiplier which is effective both in terms of speed and power. In this paper we aim to enhance the performance of the previous design. The Total Reversible Logic Implementation Cost (TRLIC) is used as an aid to evaluate the proposed design. This multiplier can be efficiently adopted in designing Fast Fourier Transforms (FFTs) Filters and other applications of DSP like imaging, software defined radios, wireless communications.

### **Keywords:**

Quantum Computing, Reversible Logic Gate, Urdhva Tiryakbhayam, Optimized Design, TRLIC.

### **1. INTRODUCTION:**

Vedic mathematics is the ancient Indian system ofmathematics which mainly deals with Vedic mathematical formulae and their application to various branches ofmathematics. Vedic mathematics was reconstructed from theancient Indian scriptures (Vedas) by Sri Bharati Krsna Tirthaafter his research on Vedas. He constructed 16 sutras and 16 upa sutras after extensive research in Atharva Veda. Themost famous among these 16 are Nikhilam Sutram, UrdhvaTiryakbhayam, and Anurupye. It has been found that UrdhvaTiryakbhayam is the most efficient among these.

Mr.V.Srinivasa Rao Associate Professor, Department of ECE, KITS for Women's, kodad, T.S, India.

The beautyof Vedic mathematics lies in the fact that it reduces otherwisecumbersome looking calculations in conventionalmathematics to very simple ones. This is so because the Vedicformulae are claimed to be based on the natural principles onwhich the human mind works. Hence multiplications in DSPblocks can be performed at faster rate. This is a very interesting field and presents some effective algorithms which can be applied to various branches of engineering. Digital signal processing (DSP) is the technology that is omnipresent in almost every engineering discipline. Fasteradditions and multiplications are the order of the day.Multiplication is the most basic and frequently used operations in a CPU. Multiplication is an operation of scaling onenumber by another. Multiplication operations also form thebasis for other complex operations such as convolution, Discrete Fourier Transform, Fast Fourier Trans forms, etc.

With ever increasing need for faster clock frequency itbecomes imperative to have faster arithmetic unit. HenceVedic mathematics can be aptly employed here to performmultiplication. Reversible logic is one of the promising fields forfuture low power design technologies. Since one of therequirements of all DSP processors and other hand helddevices is to minimize power dissipation multipliers with highspeed and lower dissipations are critical. This paper proposes an implementation of Reversible Urdhva TiryakbhayamMultiplier which consists of two cardinal features. One is them fast multiplication feature derived from Vedic algorithmUrdhva Tiryakbhayam and another is the reduced heatdissipation by the virtue of implementing the circuit usingreversible logic gates. Energy loss is an important consideration in digital circuit design. A part of this problem arises from thetechnological non ideality of switches and materials. The otherpart of the problem arises from Landauer's principle for whichthere is no solution.

Volume No: 2 (2015), Issue No: 8 (August) www.ijmetmr.com

A Peer Reviewed Open Access International Journal

Landauer's Principle states that logical computations that are not reversible necessarily generatek\*T\*ln(2) joules of heat energy, where k is the Boltzmann'sConstant k=1.38xlO-23 J/K, T is the absolute temperature atwhich the computation is performed. Although this amount ofheat appears to be small, Moore's Law predicts exponentialgrowth of heat generated due to information lost, which willbe a noticeable amount of heat loss in next decade. Also by second law of thermodynamics any processthat is reversible will not change its entropy. On thermodynamical grounds, the erasure of one bit of information from he mechanical degrees of a system must be accompanied by the thermalization of an amount of k\*T\*ln (2) joules of energy. The information entropy H can be calculated for any probability distribution. Similarly the thermodynamicentropy S refers to thermodynamic probabilities specifically. Thus gain in entropy always means loss of information, andnothing more.

Design that does not result in information loss iscalled reversible. It naturally takes care of heat generated due to information loss. Bennett showed that zero energydissipation would be possible only if the network consists ofreversible logic gates, Thus reversibility will become anessential property in future circuit design technologies. In the multiplier is designed using two units; oneis the partial product generation unit constructed using Fredkingates and other the summing unit constructed using 4x4 TSG gates. Presented a fault tolerant reversible 4x4 multipliercircuit. For construction of this circuit parity preserving FRGand MIG gates were used. Multiplier circuit was designed intwo parts. In second part of circuit MIG gates were usedinstead of half adders and full adders. Has proposed adesign of reversible multiplier which makes use of Peres gatefor generation of partial products as compared to , whichuses Fredkin gates. For the construction of adders the HNG gate was devised. Proposes low quantum cost realization f reversible multipliers which mainly uses Peres full addergate (PF AG) for its design. It also uses Peres gates for thegeneration of partial products.

### **2. REVERSIBLE LOGIC:**

Reversible logic is a promising computing designparadigm which presents a method for constructing computersthat produce no heat dissipation. Reversible computingemerged as a result of the application of quantum mechanicsprinciples towards the development of a universal computingmachine. Specifically, the fundamentals of reversiblecomputing are based on the relationship between entropy, heattransfer between molecules in a system, the probability of aquantum particle occupying a particular state at any giventime, and the quantum electrodynamics between electronswhen they are in dose proximity. The basic principle offeversible computing is that a bijective device with anidentical number of input and output lines will produce acomputing environment where the electrodynamics of thesystem allow for prediction of all future states based on knownpast states, and the system reaches every possible state, resulting in no heat dissipation.

A reversible logic gate is an N-input N-output logicdevice that provides one to one mapping between the inputand the output. It not only helps us to determine the outputsfrom the inputs but also helps us to uniquely recover theinputs from the outputs. Garbage outputs are those which donot contribute to the reversible logic realization of the design. Quantum cast refers to the cost of the circuit in terms of thecost of a primitive gate. Gate count is the number of reversiblegates used to realize the function. Gate level refers to thenumber of levels which are required to realize the given logicfunctions.

The following are the important design constraints for reversible logic circuits.

1. Reversible logic gates do not allow fan-outs.

2. Reversible logic circuits should have minimum quantum cost.

3. The design can be optimized so as to produce minimum number of garbage outputs.

4. The reversible logic circuits must use minimum number of constant inputs.

5. The reversible logic circuits must use a minimum logicdepth or gate levels.

The basic reversible logic gates encountered during the design are listed below:

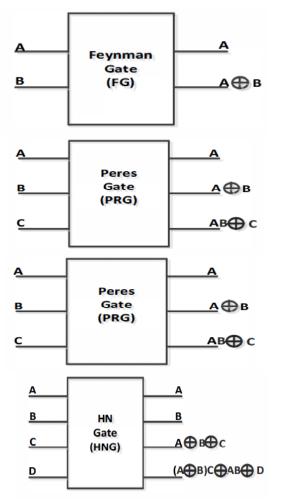

**1.Feynman Gate :** It is a 2x2 gate and its logic circuit is as shown in the figure. It is also known as Controlled Not (CNOT) Gate. It has quantum cost one and is generally used for Fan Out purposes.

**2. Peres Gate :** It is a 3x3 gate and its logic circuit is as shown in the figure. It has quantum cost four. It is used to realize various Boolean functions such as AND, XOR.

A Peer Reviewed Open Access International Journal

**3. Fredkin Gate :** It is a 3x3 gate and its logic circuit is as shown in the figure. It has quantum cost five. It can be used to implement a Multiplexer.

**4.HNG Gate:** It is a 4x4 gate and its logic circuit is as shown in the figure. It has quantum cost six. It is used for designing ripple carry adders. It can produce both sum and carry in a single gate thus minimizing the garbage and gate counts.

Figure 1: Reversible logic gates.

### 3. Urdhva – Tiryagbhyam:

Urdhva Tiryakbhayam (UT) is a multiplier based onVedic mathematical algorithms devised by ancient IndianVedic mathematicians. Urdhva Tiryakbhayam sutra can beapplied to all cases of multiplications viz. Binary, Hex andalso Decimals. It is based on the concept that generation of allpartial products can be done and then concurrent addition of these partial products is performed. The parallelism ingeneration of partial products and their summation is obtainedusing Urdhva Tiryakbhayam. Unlike other multipliers with theincrease in the number of bits of multiplicand and/ormultiplier the time delay in computation of the product doesnot increase proportionately. Because of this fact the time of computation is independent of c10ck frequency of the processor. Hence one can limit the c10ck frequency to a lowervalue. Also, since processors using lower lock frequencydissipate lower energy, it is economical in terms of powerfactor to use low frequency processors employing fastalgorithms like the above mentioned.

The Multiplier based onthis sutra has the advantage that as the number of bitsincreases, gate delay and area increases at a slow pace ascompared to other conventional multipliers.Urdhva – tiryagbhyam is the general formula applicable to all cases of multiplication and also in the division of a large number by another largenumber. It means.

Multiplication of two 2 digit numbers:

Ex.1: Find the product 14 X 12.

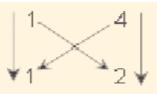

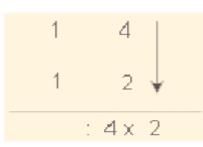

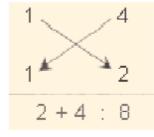

i)The right hand most digit of the multiplicand, the first number (14) i.e.,4 ismultiplied by heright hand most digit of the multiplier, the second number(12) i.e., 2. The product  $4 \times 2 = 8$  forms the right hand most part of the answer.

ii) Now, diagonally multiply the first digit of the multiplicand (14) i.e., 4 and second digit of the multiplier (12) i.e., 1 (answer 4 X 1=4); then multiply the second digit of the multiplicand i.e., 1 and first digit of the multiplier i.e., 2 (answer 1 X 2 = 2); add these two i.e., 4 + 2 = 6. It gives the next, i.e., second digit of the answer. Hence second digit of the answer is 6.

iii)Now, multiply the second digit of the multiplicand i.e., 1 and second digit of the multiplieri.e., 1 vertically, i.e., 1 X 1 = 1. It gives the left hand most part of the answer.

Thus the answer is 16 8.Symbolically we can represent the process as follows :

Volume No: 2 (2015), Issue No: 8 (August) www.ijmetmr.com

A Peer Reviewed Open Access International Journal

The symbols are operated from right to left.

### Step i) :

Step i i) :

### Step iii):

The algorithm can be illustrated using the following visualwalkthrough. Figure 2 shows the application of the algorithmfor decimal multiplication and Figure 3 for binarymultiplication.

| iai y manupi |    |         |                      |         |   |

|--------------|----|---------|----------------------|---------|---|

| 324          | R  | 20      | 324 R 14             | 4 R 14  | ł |

| 715          | PC | 00      | 715 <sub>PC</sub> 02 | 5 PC 02 | 2 |

| 0            |    | 20      | 60 16                | 50 16   | 5 |

| CARRY 2      |    |         | CARRY 1              | Y 1     |   |

| 324          | R  | 45      | 324 R 17             | 4 R 17  | , |

| 715          | PC | 01      | 715 PC 04            | 5 PC 04 | ŧ |

| 660          |    | 46      | 1660 21              | 2       | Ē |

| CARRY 4      |    |         | CARRY 2              | 2       |   |

|              |    | 324     | R 21                 | 21      |   |

|              |    | <br>715 | PC 02                | 02      |   |

|              | 2  | 31660   | 23                   | 23      |   |

|              |    |         |                      |         |   |

|              |    |         |                      |         |   |

Flgure2: urdhva tiryakbhayam algorithm fordecimal-

R is the Result and PC is the Previous Carry

Figure 3: urdhva tiryakbhayamalgorithm for binary Multiplication.

### 4.ARCHITECTURE OF REVERSIBLE URDHVA TIRYAKBHA Y AM MULIPLI-ER:

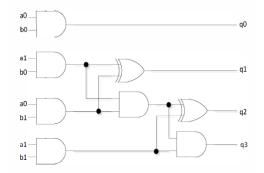

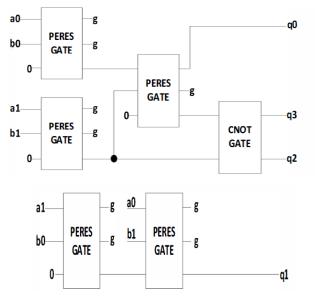

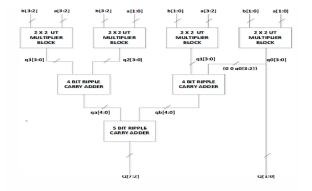

The digital logic implementation of the 2X2 UrdhvaTiryakbhayam multiplier using the conventional logic gatesis as shown in figure 4. The expressions for the fouroutput bits are given under. The reversible implementation isas shown in figure 5. This design does not consider the fanouts. The circuit requires a total of six reversible logic gatesout of which five are Peres gates and remaining one is the Feynman Gate. The quantum cost of the 2X2 UrdhvaTiryakbhayam Multiplier is enumerated to be 21. The number of garbage outputs is 9 and number of constant inputs is 4.The Reversible 4X4 Urdhva Tiryakbhayam-Multiplier design emanates from the 2X2 multiplier. Theblock diagram of the 4X4 Vedic Multiplier is presented in thefigure 6. It consists of four 2X2 multipliers each of whichproeures four bits as inputs; two bits from the multiplicandand two bits from the multiplier.

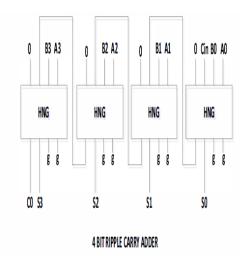

The lower two bits of theoutput of the first 2X2 multiplier are entrapped as the lowesttwo bits of the final result of multiplication. Two zeros areconcatenated with the upper two bits and given as input to thefour bit ripple carry adder. The other four input bits for theripple carry adder are obtained from the second 2X2multiplier. Likewise the outputs of the third and the terminal2X2 multipliers are given as inputs to the second four bitripple carry adder. The outputs of these four bit ripple carry adder. The outputs of these four bit ripple carry adder. 5 bits each which need to be summed up.

A Peer Reviewed Open Access International Journal

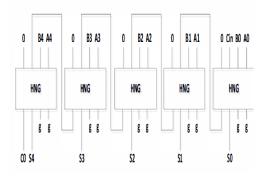

This is done by a five bit ripple carry adder which generates asix bit output. These six bits form the upper bits of the finalresult. The ripple carry adder is consummated (realized) using the HNG Gate. The number of bits that need to be ripplecarried verdicts the number of HNG gates to be used. Thus a 4bit ripple carry adder needs 4 HNG gates and the 5 bit adderrequires 5 HNG gates. This design also does not take intoconsideration the fan out gates. For this design the quantumcost is computed to be 162, the total number of gates used willbe 37, the number of garbage outputs will be 62 and thenumber of constant inputs will be 29.

The Algorithm: Multiplication of 101 by 110.

l. We will take the right-hand digits and multiply themtogether. This will give us LSB digit of the answer.

2. Multiply LSB digit of the top number by the secondbit of the bottom number and the LSB of the bottomnumber by the second bit of the top number. Once we have those values, add them together.

3. Multiply the LSB digit of bottom number with the MSB digit of the top one, LSB digit of top number with the MSB digit of bottom and then multiply thesecond bit of both, and then add them all together.

4. This step is similar to the second step, just move oneplace to the left. We will multiply the second digit of one number by the MSB of the other number.

5. Finally, simply multiply the LSB of both numberstogether to get the final product.

#### FIGURE 4: CONVENTIONAL LOGIC IMPLEMEN-TATION OF 2x2 ur MULTIPLIER

qO= aO.bO ql= (a1.bO) xor (aO.bl) q2= (aO.al.bO.bl) xor (al.bl)q3= aO.al.bO.bl

# FIGURE 5: REVERSIBLE IMPLEMENTATION OF 2x2 urMULTIPLIER

#### **5-BIT RIPPLE CARRY ADDER**

A Peer Reviewed Open Access International Journal

#### FIGURE 7: BLOCK DIAGRAM OF 4x4 UT MULTI-PLIER.

### 5. Concluding Remarks:

In this paper, a quantitative method to evaluate kinematic properties of robotic telesurgical manipulators using open surgical suturing and knot tying motion data recorded from experiments with expert surgeons is presented. Since open surgical motion data is used to evaluate the effectiveness of the system to perform suturing and knot tying tasks in minimally invasive setting, it might be desirable to segment the critical and non-critical parts of the recorded open surgical motion, especially to remove the segments corresponding to the parts of the motion when the instrument is not being actively used. This way, it possible to avoid over-conservative results. It is also important to note that this method cannot evaluate if the system will have the complete dexterity necessary, since it looks at the problem from a purely kinematic point ofview, and dexterity includes the dynamical properties of the manipulator as well as kinematics. This method not only provides the means to evaluate a kinematic design, but also helps to determine the requirements on various design parameters, such as joint ranges. In the analysis, it is also possible to move the robot with respect to the suturing site, to evaluate the suturing abilities of the system at different location and orientations in the workspace, and this can be used to find the optimal entry port location and robot configuration for optimal performance in suturing

### 6. Experimental Results:

The design of the reversible 2x2 and 4x4 multipliers is logically verified using XILINX 9.2i and MODELSIM. The simulation results are as shown in figures 10 and 11 respectively. The following are the important design constraints for any reversible logic circuits. 1. Reversible logic circuits should have minimum quantum cost.

2. The design can be optimized so as to produce minimum number of garbage outputs.

3. The reversible logic circuits must use minimum number of constant inputs.

4. The reversible logic circuits must use a minimum number of reversible gates.

### **7.ACKNOWLEDGMENTS:**

I am sk.kaiser and would like to thank the publishers, researchers for making their resources material available. I am greatly thankful to Assistant Prof: Mr.V.Srinivasa Rao for their guidance. We also thank the college authorities, PG coordinator and Principal for providing the required infrastructure and support. Finally, we would like to extend a heartfelt gratitude to friends and family members.

#### **8.REFERENCES:**

[1] Swami Bharati Krsna Tirtha, Vedic Mathematics. Delhi: Motilal Banarsidass publishers 1965

[2] Vedic Mathematics: http://www.hinduism.co.za/ve-dic.html.

[3] R. Landauer,"Irreversibility and Heat Generation in theComputational Process", IBM Journal of Research and Development, 5, pp.183-191, 1961.

[4] C.H. Bennett, "Logical reversibility of Computation", IBM J.Research and Development, pp.525-532, November 1973.

A Peer Reviewed Open Access International Journal

[5] R. Feynman, "Quantum Mechanical Computers," Optics News, Vol.11, pp. 11–20, 1985.

[6] A. Peres, Reversible logic and quantum computers, Phys. Rev. A32 (1985) 3266–3276.

[7] E. Fredkin and T. Toffoli, "Conservative Logic", Int'l J.Theoretical Physics Vol 21, pp.219-253, 1982.

[8] G Ganesh Kumarand V Charishma, Design of high speed vedicmultiplier using vedic mathematics techniques, Itn'l J. of Scientificand Research Publications, Vol. 2 Issue 3 March 2012

[9] Rakshith Saligram and Rakshith T.R. "Design of ReversibleMultipliers for linear filtering Applications in DSP" VLSICS, Vol3. No (6), Dec-12

[10] Rakshith Saligram and Rakshith T.R. "Novel Code ConverterEmploying Reversible Logic", International Journal of ComputerApplications (IJCA), August 2012.

[11] H R Bhagyalakshmi and M K Venkatesha," Optimized multiplierusing Reversible Multi-Control Input Toffoli Gates", VLSICS, Vol3. No (6), Dec.- 12

[12] Rakshith T R and Rakshith Saligram, Design of High Speed LowPower Multiplier using Reversible logic: a Vedic MathematicalApproach, Intl. Conf. on Circuit, Power and ComputationalTechnologies.

[13] H. R. Bhagyalakshmi, M. K. Venkatesha, "An Improved Design of a Multiplier using Reversible Logic Gates," IJEST, Vol. 2, No. 8,2010.

[14] Fateme Naderpour, Abbas Vafaei "Reversible Multipliers:Decreasing the Depth of the Circuit" ICECE 2008, 20-22 December 2008.

[15] Maryam Ehsanpour, Payman Moallem, Abbas Vafaei, "Design ofa Novel Reversible multiplier Circuit Using Modified Full Adder",2010 International Conference On Computer Design AndApplications, 1389, (ICCDA 2010) [16] M. Haghparast, S. Jafarali Jassbi, K. Navi and O. Hashemipour, "Design of a Novel Reversible Multiplier Circuit Using HNG Gatein Nanotechnology", World Applied Science J.IVol. 3 No. 6, 2008.

[17] M.S. Islam et al., "Low cost quantum realization of reversiblemultiplier circuit", Information technology journal, Vol.8, 2009

[18] M. Shams, M. Haghparast and K. Navi, "Novel ReversibleMultiplier Circuit in nanotechnology", World Applied ScienceJournal Vol. 3, No. 5, pp. 806-810, 2008.

[19] Nidhi Syal, Dr. H.P. Sinha, "Design of fault tolerant reversiblemultiplier", International Journal of Soft Computing andEngineering (IJSCE) ISSN: 2231-2307, Volume-1, Issue-6, January 2012.

[20] H. Thapliyal and M.B. Srinivas, "Novel Reversible MultiplierArchitecture Using Reversible TSG Gate", Proc. IEEEInternational Conference on

#### **Authors Details:**

**Ms.Sk.kaiser.** MTech student, in M.Tech Student, Dept of ECE in KITS for women's,kodad, T.S, India

**Mr.V.Srinivasa Rao** working as a Associate at ECE in KITS for women's,kodad, T.S, IndiaJNTUH Hyderabad. he has 13 years of UG/PG Teaching Experience