ISSN No: 2348-4845 International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

# Efficient Shift Register Design Using Non Overlapped Delayed Clock Pulses for Encoding and Decoding

Dr. R.Ramachandra, M.Tech., MISTE., Ph.D.,

Principal, Department of E.C.E Sri Krishnadevaraya Engineering College Gooty, Ananthapuramu Dist, (A.P)

# R S Kavitha, M.Tech (Ph.D)

Associate Professor, Department of E.C.E Sri Krishnadevaraya Engineering College Gooty, Ananthapuramu Dist, (A.P)

# ABSRACT

The architecture of a shift register is quite simple. An N-bit shift register is composed of series connected N data flip-flops. The speed of the flip-flop is less important than the area and power consumption because there is no circuit between flip-flips in the shift register. The smallest flip-flop is suitable for the shift register to reduce the area and power consumption.

This project proposes a low-power and area-efficient shift register using pulsed latches. The area and power consumption are reduced by replacing flipflops with pulsed latches. This method solves the timing problem between pulsed latches through the use of multiple non-overlap delayed pulsed clock signals instead of the conventional single pulsed clock signal. The shift register uses a small number of the pulsed clock signals by grouping the latches to several sub shifter registers and using additional temporary storage latches.

# **INTRODUCTION**

A shift register is the basic building block in a VLSI circuit. Shift registers are commonly used in many applications, such as digital filters, communication receivers, and image processing ICs. Recently, as the size of the image data continues to increase due to the high demand for high quality image data, the word length of the shifter register increases to process large image data in image processing ICs. An image-

Volume No: 3 (2016), Issue No: 8 (August) www.ijmetmr.com

# K Geetha, M.Tech (Ph.D.),

Associate Professor & HoD, Department of E.C.E Sri Krishnadevaraya Engineering College Gooty, Ananthapuramu Dist, (A.P)

## M.Bhavya Sree

M.Tech Student Department of E.C.E Sri Krishnadevaraya Engineering College Gooty, Ananthapuramu Dist, (A.P)

extraction and vector generation VLSI chip uses a 4Kbit shift register. A 10-bit 208 channel output LCD column driver IC uses a 2K-bit shift register. A 16megapixelCMOS image sensor uses a 45K-bit shift register. As the word length of the shifter register increases, the area and power consumption of the shift register become important design considerations. The architecture of a shift register is quite simple. An N-bit shift register is composed of series connected N data flip-flops. The speed of the flip-flop is less important than the area and power consumption because there is no circuit between flip-flips in the shift register. The smallest flip-flop is suitable for the shift register to reduce the area and power consumption. Recently, pulsed latches have replaced flip-flops in many applications, because a pulsed latch is much smaller than a flip-flop. But the pulsed latch cannot be used in a shift register due to the timing problem between pulsed latches.

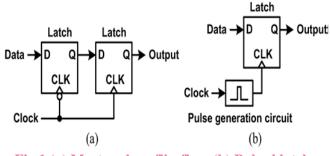

Fig.1 (a) Master-slave flip-flop. (b) Pulsed latch.

This paper proposes a low-power and area-efficient shift register using pulsed latches. The shift register

August 2016

A Peer Reviewed Open Access International Journal

solves the timing problem using multiple non-overlap delayed pulsed clock signals instead of the conventional single pulsed clock signal. The shift register uses a small number of the pulsed clock signals bygrouping the latches to several sub shifter registers and usingadditional temporary storage latches.

# **EXISTING SYSTEM**

The shift register solves the timing problem using multiple non-overlap delayed pulsed clock signals instead of the conventional single pulsed clock signal. The shift register uses a small number of the pulsed clock signals by grouping the latches to several sub shifter registers and using additional temporary storage latches.

A master-slave flip-flop using two latches can be replaced by a pulsed latch consisting of a latch and a pulsed clock signal. All pulsed latches share the pulse generation circuit for the pulsed clock signal. As a result, the area and power consumption of the pulsed latch become almost half of those of the master-slave flip-flop. The pulsed latch is an attractive solution for small area and low power consumption. The pulsed latch cannot be used in shift registers due to the timing problem.

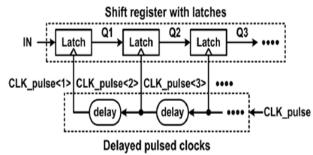

Shift Register Shift register with latches & delay circuits  $IN \rightarrow Latch \rightarrow delay \rightarrow D^2 \rightarrow delay \rightarrow 0^3 \cdots CLK_pulse \rightarrow delay \rightarrow del$

Fig. 3. Schematic of Shift register with latches, delay circuits, and a pulsed clock signal.

Volume No: 3 (2016), Issue No: 8 (August) www.ijmetmr.com One solution for the timing problem is to add delay circuits between latches, as shown in Fig. 3. The output signal of the latch is delayed and reaches the next latch after the clock pulse. As a result, all latches have constant input signals during the clock pulse and no timing problem occurs between the latches. However, the delay circuits cause large area and power overheads. Another solution is to use multiple nonoverlap delayed pulsed clock signals, as shown in Fig. 4.

The delayed pulsed clock signals are generated when a pulsed clock signal goes through delay circuits. Each latch uses a pulsed clock signal which is delayed from the pulsed clock signal used in its next latch. Therefore, each latch updates the data after its next latch updates the data. As a result, each latch has a constant input during its clock pulse and no timing problem occurs between latches. However, this solution also requires many delay circuits.

## **PROPOSED SYSTEM**

In the proposed system we are implementing the application of the shift registers in the design and implementation of the encoder and decoder.

The delayed pulsed clock signals are generated when a pulsed clock signal goes through delay circuits. Each latch uses a pulsed clock signal which is delayed from the pulsed clock signal used in its next latch. Therefore, each latch updates the data after its next latch updates the data. As a result, each latch has a constant input during its clock pulse and no timing problem occurs between latches.

# **Master Slave Clocking**

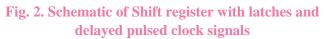

Gigabit Ethernet transceivers operate in a "loop timed "fashion (Fig. 10). This means that the transceivers at the two ends of a link assume two different roles as far as synchronization is concerned. One of them, called the master, transmits data using an independent clock GTX-CLK provided through the GMII interface (in actuality the transmit clock used by the master may be a filtered version of GTX-CLK, obtained using a phase locked loop with a very narrow bandwidth, to reduce jitter). The other side, called the slave, synchronizes its receive and transmit clocks to the signal received from the master, using its timing recovery system. The slave ISSN No: 2348-4845 International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

transmit clock maintains a fixed phase relationship with the slave receive clock at all times. Then, the receive clock at the master synchronizes with the signal received from the slave. Thus, after an initial acquisition period, the master receive clock will follow the master transmit clock with a phase difference determined by the round trip delay of the loop. This phase relationship may vary dynamically as a result of the need of the master receive clock to track jitter present in the signal received from the slave.

# DIFFERENCE BETWEEN LATCHES AND FLIP FLOPS:

Latches and flip flops are the basic elements and these are used to store information. One flip flop and latch can store one bit of data. The main difference between the latches and flip flops is that, a latch checks input continuously and changes the output whenever there is a change in input. But, flip flop is a combination of latch and clock that continuously checks input and changes the output time adjusted by the clock. In this article, we are going to look at the operations of the numerous latches and flip-flops.

# **Latches and Flip Flops**

Both Latches and flip flops are circuit elements wherein the output not only depends on the current inputs, but also depends on the previous input and outputs. The main difference between the latch and flip flop is that a flip flop has a clock signal, whereas a latch does not. Basically, there are four types of latches and flip flops: SR, D, JK and T. The major differences between these types of flip flops and latches are the number of i/ps they have and how they change the states. There are different variations for each type of latches and flip-flops which can enhance their operations.

#### **EXPERIMENTAL STUDY**

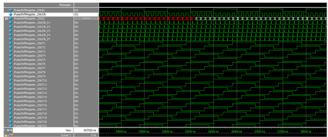

Fig1: The pulsated latches shift register result

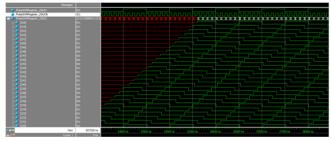

Fig2: the pulsed latches shift register result

The result was achieved by combining 4-bit shift registers in parallel manner. We are using total 64 stages of 4- bit shift registers. Each 4-bit shift registers using 5 latches in total. We are showing the nonoverlapped multiple pulsed clock pulses using the delayed clock pulse generator unit. We are showing the shift registers output in the final output.

# CONCLUSION

This project proposed a low-power and area-efficient shift register using pulsed latches. The shift register reduces area and power consumption by replacing flipflops with pulsed latches. The timing problem between pulsed latches is solved using multiple non-overlap delayed pulsed clock signals instead of a single pulsed clock signal. A small number of the pulsed clock signals is used by grouping the latches to several sub shifter registers and using additional temporary storage latches.

# **FUTURE SCOPE:**

In future, we can use this shift registers using pulsed latches to design the encoders and decoders. Those encoders are very much useful in encryption and decryption techniques, which are useful in security applications. Besides that we can also increase the bit size of the shift register for faster operations and for more robust secure applications.

ISSN No: 2348-4845 International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

## REFERENCES

[1] P. Reyes, P. Reviriego, J. A. Maestro, and O. Ruano, "New protectiontechniques against SEUs for moving average filters in a radiation environment,"IEEE Trans. Nucl. Sci., vol. 54, no. 4, pp. 957–964, Aug.2007.

[2] M. Hatamianet al., "Design considerations for gigabit ethernet 1000base-T twisted pair transceivers," Proc. IEEE Custom Integr. CircuitsConf., pp. 335–342, 1998.

[3] H. Yamasaki and T. Shibata, "A real-time image-feature-extraction andvector-generation vlsi employing arrayed-shift-register architecture,"IEEE J. Solid-State Circuits, vol. 42, no. 9, pp. 2046–2053, Sep. 2007.

[4] H.-S. Kim, J.-H. Yang, S.-H. Park, S.-T. Ryu, and G.-H. Cho, "A 10-bitcolumn-driver IC with parasiticinsensitive iterative charge-sharingbased capacitorstring interpolation for mobile active-matrix LCDs,"IEEE J. Solid-State Circuits, vol. 49, no. 3, pp. 766–782, Mar. 2014.

[5] S.-H. W. Chiang and S. Kleinfelder, "Scaling and design of a 16-megapixelCMOS image sensor for electron microscopy," in Proc. IEEENucl. Sci. Symp. Conf. Record (NSS/MIC), 2009, pp. 1249–1256.

[6] S. Heo, R. Krashinsky, and K. Asanovic, "Activitysensitive flip-flopand latch selection for reduced energy," IEEE Trans. Very Large ScaleIntegr. (VLSI) Syst., vol. 15, no. 9, pp. 1060–1064, Sep. 2007.

[7] S. Naffziger and G. Hammond, "The implementation of the nextgeneration64 b itanium microprocessor," in IEEE Int. Solid-State CircuitsConf. (ISSCC) Dig. Tech. Papers, Feb. 2002, pp. 276–504.

[8] H. Partoviet al., "Flow-through latch and edgetriggered flip-flop hybridelements," IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech.Papers, pp. 138–139, Feb. 1996.

[9] E. Consoli, M. Alioto, G. Palumbo, and J. Rabaey, "Conditionalpush-pull pulsed latch with 726 fJops energy delay product in 65 nmCMOS," in IEEE Int.

Volume No: 3 (2016), Issue No: 8 (August) www.ijmetmr.com

Solid-State Circuits Conf. (ISSCC) Dig. Tech.Papers, Feb. 2012, pp. 482–483.

[10] V. Stojanovic and V. Oklobdzija, "Comparative analysis of masterslavelatches and flip-flops for high-performance and low-power systems,"IEEE J. Solid-State Circuits, vol. 34, no. 4, pp. 536–548, Apr.1999.

# **Author Details**

M.Bhavya Sree M.Tech Student Department of E.C.E Sri Krishnadevaraya Engineering College Gooty, Ananthapuramu Dist, (A.P)

## **R S Kavitha, M.Tech (Ph.D)**

Associate Professor, Department of E.C.E Sri Krishnadevaraya Engineering College Gooty, Ananthapuramu Dist, (A.P)

# K Geetha, M.Tech (Ph.D.),

Associate Professor & HoD, Department of E.C.E Sri Krishnadevaraya Engineering College Gooty, Ananthapuramu Dist, (A.P)

Dr. R.Ramachandra, M.Tech., MISTE., P.hD.,

Principal, Department of E.C.E Sri Krishnadevaraya Engineering College Gooty, Ananthapuramu Dist, (A.P)