A Peer Reviewed Open Access International Journal

# A New Gate for Low Cost Design of All Optical Reversible Logic Circuit

S T Mrudula, M.Tech, (Ph.D)

Associate Professor

Department of ECE

Sri Krishnadevaraya Engineering College,

Gooty.

#### Abstract:

The development in the field of nanometer technology leads to minimize the power consumption of logic circuits. Reversible logic design has been one of the promising technologies gaining greater interest due to less dissipation of heat and low power consumption. Recently, in the literature, reversible logic gates and combinational circuits have been proposed in optical domain using Semiconductor Optical Amplifier (SOA) based Mach Zehnder interferometer (MZI) switches due to its significant advantages such as high speed, low power, fast switching and ease of fabrication. Optical reversible designs have used ad-hoc approaches and require high cost in terms of MZI switches, Beam Splitters (BS), and Beam Combiners (BC) as well as optical delay. In this work, an optical reversible MNOT gate and all-optical realization of 4×4 Toffoli Gate have been proposed which is used in all-optical realization of optimized reversible combinational circuits. A general design approach to realize all-optical reversible circuits based on MZI switches has been proposed first time in the literature. Optimized alloptical reversible 2×1 multiplexer and full adder circuits have been designed using these proposed gates and design approach. All-optical reversible designs of 4×1 multiplexer, 1×4 Demultiplexer and 3to8 Decoder circuits have also been presented in this work first time in the literature. Our results have shown significant improvements over existing designs in terms of MZI switches, BS, BC and optical delay.

Keywords—Optical Reversible computing; Mach-ZehnderInterferometer(MZI); Full Adder; Multiplexer; Decoder; optical cost.

M. Pranitha

M.Tech (VLSI)

Department of ECE

Sri Krishnadevaraya Engineering College,

Gooty.

#### **INTRODUCTION:**

The growing technologies have increased the demand of high performance computing. According to G. Moore's low [1], number of transistor counts to be integrated per unit area in devices will almost double in one and half year. To achieve high speed computation, high packaging density in the logic circuits is required which results in more heat dissipation.

The conventional computing is found unable to deal with low power, high compaction and heat dissipation issues of the current computing environment. In 1961, R. Laundaur [2] stated that heat dissipation occurs due to energy loss in irreversible logics. Each bit of information dissipates an amount of energy equal to KTln2 joules where K is Boltzmann's Constant and T is the absolute temperature. In 1973, C. H. Bannett [3] stated that reversible logic can overcome the heat dissipation problem of VLSI circuits because the bits of information are not erased in reversible computing. New technologies are emerging to deal with these issues. Reversible Computing is one way to overcome the problem of heat dissipation in computing chips which in turn help in increasing the packaging density. Reversible Logic seems to be hopeful due to its wide application in emerging technologies such as quantum computing, optical computing and power efficient nanotechnologies etc. Reversible circuits do not lose information. A reversible logic gate has one to one mapping between input and output vectors i.e. number of input lines are equal to number of output lines in the reversible gate [12], [14]. Fan-out is not permitted in the reversible logic. Constant inputs and garbage output

A Peer Reviewed Open Access International Journal

line can be added to the circuit to make it reversible[12], [13], [14].

Optical Computing is computation with photon as opposed to conventional electron based computation. Unmatched high speed and zero mass of photon have attracted the researchers towards the optical realization of reversible logic gates using Semiconductor Optical Amplifier (SOA) based Mach Zehnder Interferometer (MZI) switches. MZI Switches are preferred because of its high speed, fast switching, low power and ease in fabrication [4], [5], [6]. The authors have presented the optical realization of popular reversible logic gates such as Feynman and Toffoli Gates [4], Fredkin Gate [5], and Peres Gate [6] etc. All-optical reversible combinational circuits for instance 2×1 Multiplexer [7], Binary Ripple Carry Adder [8], NOR Gate [9], New Gate [10], Hybrid New Gate (HNG) [11] and Modified Fredkin Gate [15] etc. are proposed by the authors in the literature.

In this paper, we have proposed an optical reversible MNOT gate using one MZI switch. All-optical realization of 4×4 Toffoli Gate has been presented which is used in alloptical realization of optimized reversible combinational circuits. A general design approach to realize all-optical reversible circuits based on MZI switches has been proposed first time in the literature. Optimized all-optical reversible 2×1 multiplexer and full adder circuits have been designed using these proposed gates and design approach. Alloptical reversible designs of 4×1 multiplexer, 1×4 D emultiplexer and 3to8 Decoder circuits have also been presented in this work first time in the literature. Our results have shown significant improvements over existing designs in terms of MZI switches, BS, BC and optical delay.

# BASICS OF ALL OPTICAL REVERS IBLE LOGIC

Reversible logics are implemented with optical technology using some building blocks such as MZI based optical switch, beam splitter and beam combiner.

#### **SOA Based MZI Switch**

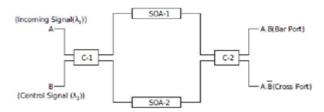

An SOA based MZI switch can be de signed using two Semiconductor Optical Amplifiers (SOA-1, SOA-2) and two couplers (C -1, C-2) [8], [9]. In an MZI switch, there are two inputs ports A and B, and two output ports called bar port and cross port, respectively, as shown in Figure 1 and 2.

Fig. 1. Block diagram of Mach-Zehnder Interferometer switch [8]

Fig. 2. SOA based Mach-Zehnder Interferometer switch [8]

The optical signal at port B is termed as the control signal and signal at port A is termed as incoming signal. When there are signals present at port A and port B then there is a presence of light signal at the bar port an d absence of light signal at the cross port. In the absence of co ntrol signal at port B and presence of incoming signal at port A, the outputs of MZI are interchanged and results in the presence of light at the cross port and no light at the bar port. Here, absence of light is considered as the logic value 0 and p resence of light is considered as logic value 1. This behavior of SOA based MZI switch can be written as Boolean functions having inputs to outputs mapping as (A, B)  $\rightarrow$  (P=A.B, Q = A.B ), where A, B are the inputs and P, Q are the outputs of MZI, respectively. The optical cost and the delay ( ) of MZI based all optical switch is considered as unity. The authors have considered the following optimization parameters for the all-optical reversible logics: optical cost i.e. number of MZI switches, number of BC and BS used in the logic

A Peer Reviewed Open Access International Journal

circuit, and optical delay i.e. number of stages of MZI switches used in the design of logic circuit.

#### **All-optical Feynman gate:**

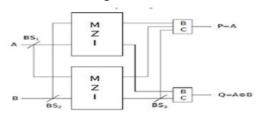

The Feynman gate (FG) has mapping (A, B)  $\rightarrow$  (P=A, Q=A $\oplus$ B) where A, B are the inputs and P=A, Q=A $\oplus$ B are the outputs, respectively. The Feynman gate can be realized using 2 MZI switches, 2 bea m combiners (BC) and 3 beam splitters (BS) in all optical domain as shown in figure 3 [4].

Fig. 3. Feynman gate and its all-optical implementation [4]

# PROPOSED ALL-OPTIC AL REVERSIBLE LOGIC GATE

We have proposed a new M NOT gate and presented an all-optical realization of 4×4 Toffoli Gate which are efficient to design optimized optical reversible circuits.

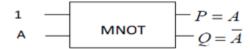

Proposed all-optical reversible MNOT Gate:

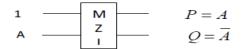

A new  $2\times2$  all-optical reversible MNOT gate  $(1, A) \rightarrow (P, Q)$  has been proposed, where P = A and Q = A. Figure 4 shows the Block diagram of M NOT gate. This gate generates logical NOT of the input logic A. Table I shows the truth table of MNOT gate.

Fig. 4. Block diagram of Proposed 2×2 MNOT gate

# TABLE I TRUTH TABLE OF THE PROPOSED REVERSIBLE GATE

| Inp | out | Ou    | tput               |

|-----|-----|-------|--------------------|

| 1   | A   | P = A | $Q = \overline{A}$ |

| 1   | 0   | 0     | 1                  |

| 1   | 1   | 1     | 0                  |

The all-optical reversible MNOT gate has been shown in figure 5. This gate is designed with single MZI switch. The incoming signal of MZI switch is set to 1 then output generated at cross port is inverse of the input at control signal.

The optical cost of MNOT gate is one. NO Beam Splitter (BS) or Beam Combiner (BC) is used in this gate. As only one MZI switch is used, so the delay is 1 A

Fig. 5. Proposed 2×2 Optical Reversible MNOT gate

The optical MNOT gate is a useful logic gate in alloptical reversible circuit realization. Earlier the authors has used Feynman gate to generate inverse of logic with optical cost 2 MZI switches. Using this gate cost has been reduced to one MZI switch.

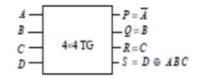

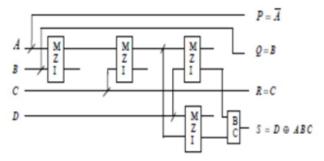

#### Optical Realization of 4×4 Toffoli Gate

The  $4\times4$  Toffoli Gate  $(4\times4$  TG) is mapped from input vector (A, B, C, D) to output vector (P, Q, R, S), where P=A, Q=B, R=C, and S=D  $\bigoplus$ ABC, respectively. Basically,  $4\times4$  Toffoli gate is Multiple Controlled Toffoli gate (MCT) with 3

Fig. 6. Block diagram of 4×4 Toffoli gate

Fig. 7. All-optical Realization of 4×4 Toffoli gate control lines.

A Peer Reviewed Open Access International Journal

Figure 6 shows the Block dia gram and Figure 7 Shows the all -optical realization of  $4\times4$  Toffoli gate. This gate has been realized with 4 MZI Switches, Five Beam splitters (BS) and one Beam Combiners (BC). The optical delay of this gate is considered as  $3\Delta$ .

#### PROPOSED GENERAL DESIGN A PPROACH

We have realized optical reversible circuits using MZI switches in different ways. No specified approach is followed in the synthesis of the all -optical reversible circuits. In this work, we have proposed a general design approach to realize all-optical reversible circuits. The approach is described as follows:

# Algorithm 1: Design approach to realize optical reversible circuits

Step1. Consider the desired combinational logic circuit Step2.IF the desired logic function is complex then Step3.Apply Replacement Method

Step4. ELSE apply Truth Table based Method with desired output logic function

Step5. Realize the optical reversible logic circuit

#### **Algorithm 2: Replacement Method**

Step1. Repeat step 2 to 6 WHILE all the gates in the conventional logic circuit are replaced

Step2. Choose a logic gate from conventional circuit

Step3. IF equivalent optical reversible gate is already existed then

Step4. Replace the chosen gate with equivalent gate

Step5. ELSE design the required optical reversible logicgate with truth table based method

Step6. Replace the chosen gate with this designed gate

#### Algorithm 3: Truth table Based method

Step1. Derive the desired output logic function from the truth table of the circuit

Step2. Add constant inputs and garbage output lines tomake it reversible if needed

Step3. Design the all-optical reversible circuit using MZIswitches, Beam Splitters and Beam Combiners realizing the logic functions at output lines

# PROPOSED ALL-OPTICA L REVERSIBLE LOGIC CIRCUITDESIGNS

#### Proposed All-optical Reversible 2×1 Multi<del>p</del>lexer

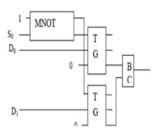

This section describes the design and realization of the reversible  $2\times1$  Multiplexer in all-optical domain using the proposed MNOT gate and optical Toffoli Gate (TG) [4]. It has two data inputs (D<sub>0</sub> and D<sub>1</sub>), a single output O and a select line S<sub>0</sub> to select one of the two input data lines. The outputfunction of  $2\times1$  Multiplexer is given by  $O = S_0D_0 + S_0D_1$ .

# TABLE II TRUTH TABLE OF 2×1 MULTIPLEXER

|                | Input | Output |   |

|----------------|-------|--------|---|

| D <sub>0</sub> | $D_1$ | So     | 0 |

| 0              | 0     | 0      | 0 |

| 0              | 0     | 1      | 0 |

| 0              | 1     | 0      | 0 |

| 0              | 1     | 1      | 1 |

| 1              | 0     | 0      | 1 |

| 1              | 0     | 1      | 0 |

| 1              | 1     | 0      | 1 |

| 1              | 1     | 1      | 1 |

The truth table of  $2\times1$  Multiplexer is shown in table II. The optical realization of  $2\times1$  Reversible Multiplexer is shown in figure 8. It is designed with one MNOT and two TG gates. Here, MNOT gate behaves as NOT gate. When the third input line of TG is set to Constant 0 (Zero), the TG behaves as AND gate.

Fig. 8. Optical Realization of 2×1 Reversible Multiplexer

The MNOT gate is made of 1 MZI Switch. No BS and BC are used in the design of MNOT gate. The TG is made of 3 MZI Switches, 4 BS and one BC [4]. The delay of MNOT gate is  $1\Delta$  and that of TG is  $2\Delta$ . Thus, total optical cost of Optical Reversible  $2\times1$  Multiplexer is 7 MZI Switches; total Beam splitters used are 8; beam Combiners used are 3 and Delay of

A Peer Reviewed Open Access International Journal

the multiplexer circuit is calculate d as  $3\Delta$  as the two TG are working in parallel. It can be observed that optical cost of the Optical Reversible  $2\times1$  Multiplexer h as been improved significantly in compare to existing one [7] which was implemented using 8 MZI switches, 12 Beam splitters, 5 Beam combiners, and optical delay  $3\Delta$ .

#### **Proposed All-optical Reversible Full Adder Circuit**

This section describes a design of all-Optical reversible full Adder circuit using two existing all-Optical Reversible Logic gates with improved Optical cost. The truth table of the full adder circuit is shown in the table III. The output functions of Full Adder circuit are given as follows:

$S = A \oplus B \oplus C$  ;  $C_{out} = AB + (A \oplus B) C$

# TABLE III TRUTH TABLE OF THE FULL ADDER CIRCUIT

| ] | Input | Output |   |     |

|---|-------|--------|---|-----|

| A | В     | C      | S | Cov |

| 0 | 0     | 0      | 0 | 0   |

| 0 | 0     | 1      | 1 | 0   |

| 0 | 1     | 0      | 1 | 0   |

| 0 | 1     | 1      | 0 | 1   |

| 1 | 0     | 0      | 1 | 0   |

| 1 | 0     | 1      | 0 | 1   |

| 1 | 1     | 0      | 0 | 1   |

| 1 | 1     | 1      | 1 | 1   |

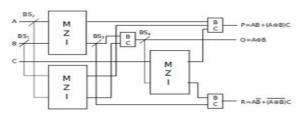

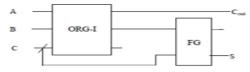

The new improved Optical Reversible F ull Adder circuit is designed using two existing all-optical reversible logic gates; One is Optical Feynman Gate which is mapped as  $(A, B) \rightarrow (P,Q)$  where P=A and  $Q=A \oplus B$ , and another is ORG-I [8] which is mapped as  $(A, B, C) \rightarrow (P, Q, R)$  where  $P=AB+(A \oplus B)C,Q=A \oplus B$  and  $R=A\overline{B}+(A \oplus B)C$ .

The ORG-I gate is shown in the Figure 9. The improved all-optical reversible full adder is shown in the figure 10. Input bit A, B and C are passed at three inputs of the ORG-I gate. The output P of ORG-I implements the output carry function of Full adder; Output Q of ORG-I and input C are passed to input lines of Feynman gate which produces output Sum Function of Full Adder.

Fig. 9. Optical Reversible Gate (ORG)-I [8]

The ORG-I has 3 MZI switches, 4 BS and 3 BC with optical delay as  $2\Delta$ . The Feyn man Gate is realized with 2MZI switches, 3 BS, 2 BC and optical delay is  $1\Delta$ . Thus, it can be observed from the figure that All-Optical Reversible Full Adder is realized with 5 MZI switches, 8 Beam Splitters and 5

Fig. 10.The improved All- Optical Reversible Full Adder

Beam Combiners. The optical delay is considered as  $3\Delta$ . It can be seen that the optical cost of the All-Optical Reversible Full Adder Circuit is improved significantly compared to the existing design of Full adder circuit [8] in terms of MZI switches and Beam Combiners.

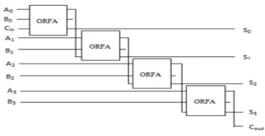

#### 4-bit Optical Reversible Full Adder Circuit

A 4-bit optical reversible full adder circuit is designed using 4 ORFA (optical reversible full adder). The diagram of the 4-bit optical reversible full adder is shown in the Figure 11. The carry output of first ORFA is passed to carry input of second ORFA, carry output of second ORFA is passed to carry input of third ORFA and so on.

Fig. 11.4-bit Optical Reversible Full Adder Circuit

A Peer Reviewed Open Access International Journal

Finally the carry output line of the fourth ORFA produces output carry of addition of two 4-bit numbers. The sum output line of all he ORFA collectively produces 4-bit sum of two 4-bit numbers. Optical cost of the circuit is 20 MZI switches as each ORFA is designed with 5 MZI switches, 8 Beam Splitters and 5 Beam Combiners. Thus, total 32 BS and 20 BC are used in the design of 4-bit optical reversible full adder. The optical delay of the circuit is 12Δ.

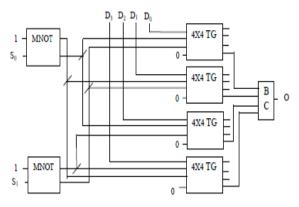

#### Design of Optical Reversible 4×1 Multiplexer

This is first attempt in the literature for designing all-Optical Reversible  $4\times1$  multiplexer circuit. The all-optical Reversible  $4\times1$  Multiplexer circuit has been realized with proposed Optical Reversible MNOT gate and Optical  $4\times4$  Toffoli Gate  $(4\times4$  TG). It has four data input lines  $(D_0-D_3)$ , two selection lines  $S_0$  and  $S_1$  to select one of the four inputs and a single output line O. the expression for data output O is given as

$$O = D_{\bullet} \overline{S_{\bullet}} \overline{S_{\downarrow}} + D_{\downarrow} S_{\bullet} \overline{S_{\downarrow}} + D_{\downarrow} \overline{S_{\bullet}} S_{\downarrow} + D_{\downarrow} S_{\bullet} S_{\downarrow}$$

The truth table of  $4\times1$  Multiplexer is shown in table IV . The optical realization of the  $4\times1$  Reversible Multiplexer is shown in the figure 12. It is designed using two MNOT gates and four optical  $4\times4$  TG gates. The fourth input lines of all the  $4\times4$  TG are set to constant 0, which results in Logical AND of the remaining three inputs at fourth output line of  $4\times4$  TG. The fourth output lines of all the  $4\times4$  TG are combined using Beam Combiner (BC) at the final output. The MNOT gate is designed with 1 MZI Switch. No BS and BC are used in the design of MNOT gate. The  $4\times4$  TG is realized with four M ZI Switches, Five Beam splitters (BS) and one Beam Combiners (BC). The delay of this gate is considered as  $3\Delta$ .

Thus, the optical cost of the all -optical  $4\times1$  Reversible Multiplexer circuit comes out to be 18 MZI Switches, 24 BS, 5 BC. The delay is calculated  $4\Delta$  as two MNOT gates as well as four  $4\times4$  T G are working in parallel.

TABLE IV THE TRUTH TABLE OF 4×1 MULTIPLEXER

| Input |                | Output         |

|-------|----------------|----------------|

| $S_1$ | S <sub>0</sub> | 0              |

| 0     | 0              | D <sub>0</sub> |

| 0     | 1              | $D_1$          |

| 1     | 0              | $D_2$          |

| 1     | 1              | D <sub>3</sub> |

Fig. 12. Design of 4×1 Optical Reversible Multiplexer

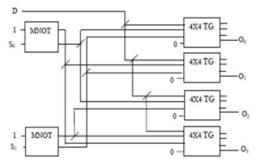

#### Design of Optical Reversible 1×4 De-Multiplexer

Authors, in the literature, have not yet designed any single Reversible  $1\times4$  De-Multiplexer in optical domain. This is first time, an All -optical Reversible  $1\times4$  De-Multiplexer has been proposed. It has one input data line D, 2 select input lines (S<sub>0</sub> and S<sub>1</sub>) and four output lines (O <sub>0</sub>- O<sub>3</sub>). The truth table of  $1\times4$  De-Multiplexer is shown in table V. The expression for output lines are given as follows:

$$O_0 = D\overline{S_1}\overline{S_0}$$

,  $O_1 = D\overline{S_1}S_0$ ,  $O_2 = DS_1\overline{S_0}$  and  $O_3 = DS_1S_0$

For optical realization of Reversible 1×4 De-Multiplexer, transformation based approach is used. The Optical Reversible 1×4 De-Multiplexer is designed with optical MNOT gate and optical 4×4 TG gates. The logical NOT Gate and the logical AND are replaced with proposed optical reversible MNOT gate and 4×4 TG, respectively. Optical realization is shown in Figure 13.

A Peer Reviewed Open Access International Journal

#### TABLE V TRUTH TABLE OF 1×4 DE-MULTIPLEXER

| Inp | Input |    | Output |    |    |  |  |

|-----|-------|----|--------|----|----|--|--|

| Sı  | So    | 0: | O2     | Oı | 00 |  |  |

| 0   | 0     | 0  | 0      | 0  | D  |  |  |

| 0   | 1     | 0  | 0      | D  | 0  |  |  |

| 1   | 0     | 0  | D      | 0  | 0  |  |  |

| 1   | 1     | D  | 0      | 0  | 0  |  |  |

Fig. 13. Optical realization of reversible 1×4 De-Multiplexer

It can be observed that 2 optical MNOT gates and four  $4\times4$  TG gates have been used in optical realization of  $1\times4$  De-Multiplexer. This circuit is designed using 18 MZI Switches, 27 Beam Splitters and 4 Beam Combiners. Two MNOT Gates as well as four  $4\times4$  TG are connected in parallel. Thus, Delay is calculated as  $4\Delta$ .

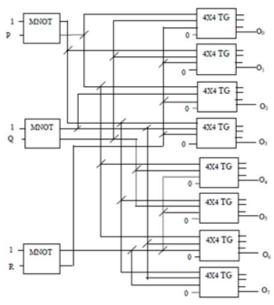

#### **Design of Optical Reversible 3to8 Decoder**

A Decoder circuit is similar to the De- Multiplexer circuit but there is no data input line. This is also first time attempt in the literature to design an all- Optical Reversible 3to8 Decoder circuit. A 3to8 Decoder has three input li nes (P, Q, R) and eight output lines  $(O_0 - O_7)$ . The truth table of 3to8 decoder has been given in table VI. The output function of the 3to8 Decoder is expressed as follows:

$$O_0 = \overline{PQR}$$

;  $O_1 = \overline{PQR}$ ;  $O_2 = \overline{PQR}$ ;  $O_3 = \overline{PQR}$

$$O_4 = PQR$$

;  $O_5 = PQR$ ;  $O_6 = PQR$ ;  $O_7 = PQR$

Optical reversible 3t08 decoder design using proposed MNOT gate and Optical 4×4 T G. To realize this circuit, three MNOT gates and eight 4×4 TG gates are needed. The all-Optical realization of the reversible

3to 8 Decoder is shown in the figure 14. The circuit is designed with 35 MZI switches, 58 Beam Splitters and 8 Beam Combiners. Delay of the circuit is  $4\Delta$ .

# TABLE VI TRUTH TABLE OF 3TO8 DEC ODER

|   | Input |   | Output |    |    |    |    |    |    |    |

|---|-------|---|--------|----|----|----|----|----|----|----|

| P | Q     | R | 00     | 01 | 02 | 03 | 04 | 05 | 06 | 07 |

| 0 | 0     | 0 | 1      | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0 | 0     | 1 | 0      | 1  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0 | 1     | 0 | 0      | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

| 0 | 1     | 1 | 0      | 0  | 0  | 1  | 0  | 0  | 0  | 0  |

| 1 | 0     | 0 | 0      | 0  | 0  | 0  | 1  | 0  | 0  | 0  |

| 1 | 0     | 1 | 0      | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| 1 | 1     | 0 | 0      | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| 1 | 1     | 1 | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

Fig. 14. All-Optical realization of the reversible 3to8

Decoder

#### **COMPARISION RESULTS**

The optical cost and optical propagation delay of the proposed all-optical reversib le logic circuits have been calculated in the previous section. Here the same have been analyzed and a summery has been presented in the following tables. Comparative studies of proposed designs of all-optical reversible 2×1 multiplexer and full adder circuits with the existing designs are presented in table VII and VIII respectively. This

A Peer Reviewed Open Access International Journal

comparison is based on the optimization parameters such as optical cost, beam splitters, beam combiners, and optical delay of the circuits. The improvement percentage (IP) is calculated using the formulae: (1-proposed design cost/existing design cost) ×100. It can be observed that the proposed designs have been optimized in terms of MZI switch BS and BC.

## TABLE VII COMPARATIVE STUDY OF ALL OPTICAL REVERSIBLE 2×1

| Proposed              | MZI       | BS        | BC        | Optical   |  |  |

|-----------------------|-----------|-----------|-----------|-----------|--|--|

| Design                | Switch    | {IP in %} | {IP in %} | delay     |  |  |

|                       | {IP in %} |           |           | {IP in %} |  |  |

| Our proposed          | 7         | 8         | 3         | 3∆        |  |  |

| design                | {12.5%}   | (33.33%)  | {40%}     | {No IP}   |  |  |

| G. K. Maity et<br>al. | 8         | 12        | 5         | 3Δ        |  |  |

TABLE VIII COMPARATIVE STUDY OF ALL-OPTICAL REVERSIBLE FULL ADDER CIRCUIT

| Proposed      | MZI       | BS        | BC        | Optical   |

|---------------|-----------|-----------|-----------|-----------|

| Design        | Switch    | {IP in    | {IP in %} | delay     |

|               | {IP in %} | %}        |           | {IP in %} |

| Our proposed  | 5         | 8         | 5         | 3∆        |

| design        | {16.66%}  | { No IP } | {16.66%}  | {No IP }  |

| S. Kotiyal et |           |           |           | 2.        |

| al.           | 6         | 8         | 6         | 3Δ        |

All-optical reversible designs of 4×1 multiplexer, 1×4 De-multiplexer and 3to8 Decoder circuits are proposed first time, therefore, optical cost and optical delay of the these circuits have been presented in table IX.

# TABLE IX OPTICAL COST AND DELAY OF ALL-OPTICAL REVERSIBLE 4×1 MULTIPLEXER, 1×4 DE-MULTIPLEXER AND 3TO8 DECODER

| Proposed Design        | MZI<br>Switch | BS | BC | Optical delay |

|------------------------|---------------|----|----|---------------|

| 4×1 multiplexer        | 18            | 24 | 5  | 4∆            |

| 1×4 De-<br>multiplexer | 18            | 27 | 4  | 4∆            |

| 3to8 Decoder           | 35            | 58 | 8  | 4∆            |

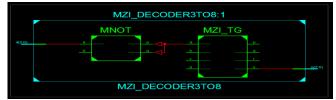

#### SIMULATION RESULTS

All the synthesis and simulation results are performed using Verilog HDL. The synthesis and simulation are performed on Xilinx ISE 14.4. The simulation results are shown below figures.

Fig.15: RTL schematic of All-Optical realization of the reversible 3to8 Decoder

Fig.16: RTL sub schematic of All-Optical realization of the reversible 3to8 Decoder

Fig.17: Technology schematic of All-Optical realization of the reversible 3to8 Decoder

Fig.18: Simulation of All-Optical realization of the reversible 3to8 Decoder

#### **CONCLUSION AND FUTURE SCOPE**

Optical computing is emerging as a feasible technology to implement reversible logic. We have proposed a new general design approach to realize alloptical reversible logic circuits using SOA based MZI switches. An all-optical reversible MNOT gate has been proposed. The optical costs of the all

A Peer Reviewed Open Access International Journal

opticalreversible 2×1 multiplexer and full adder circuits have been minimized in the proposed designs. A 4-bit full adder circuit has been also designed using this full adder circuit. New designs of All-optical reversible designs of 4×1 multiplexer, 1×4 Demultiplexer and 3to8 Decoder circuits are proposed first time. An optimization algorithm may be proposed to minimize the optical cost of the all optical reversible circuits and the existing designs may be optimized. All –optical reversible sequential circuits may be designed.

#### REFERENCES

- [1] Moore, Gordon. "The Future of Integrated Electronics." Fairchild Semiconductor internal publication, 1964.

- [2] R. Landauer, "Irreversibility and heat generation in the computing process", IBM Journal of Research and Development, pp. 183–191, July 1961

- [3] C. H. Bennet, "Logical Reversibility of Computation", IBM Journal of Research and Development, vol. 17, no. 6, pp. 525-532, 1973

- [4] C. Taraphdara, T. Chattopadhyay, and J. Roy, "Mach-zehnder interferometer-based all-optical reversible logic gate", Optics and Laser Technology, vol. 42, no. 2, pp. 249–259, 2010.

- [5] G. K. Maity, S. P. Maity, T. Chattopadhyay and J. N. Roy, "MachZehnder Interferometer Based All-Optical Fredkin Gate", International Conference on Trends in Optics and Photonics March 1 4, 2009 Kolkata, India Department of Applied Optics and Photonics University of Calcutta, Kolkata, India.

- [6] G. K. Maity, J. N. Roy, and S. P. Maity, "Machzehnder interferometer based all-optical peres gate", in Advances in Computing and Communications, ser. Communications in Computer and InformationScience, A. Abraham, J. L. Mauri, J. F. Buford, J. Suzuki, and S. M. Thampi, Eds. Springer Berlin Heidelberg, 2011, vol. 192, pp. 249–258.

- [7] G. K. Maity, T. Chattopadhyay, J. N. Roy, and S.P. Maity, "All-optical reversible multiplexer", Computers and Devices for Communication, 2009. CODEC 2009. 4th International Conference on , vol., no., pp.1,3, 14-16 Dec. 2009

- [8] S. Kotiyal, H. Thapliyal, and N. Ranganathan, "Mach-zehnder interferometer based design of all optical reversible binary adder", in Design, Automation Test in Europe Conference Exhibition (DATE),2012, pp. 721–726, March 2012.

- [9] S. Kotiyal, H. Thapliyal, and N. Ranganathan, "Mach-Zehnder Interferometer Based All Optical Reversible NOR Gates", VLSI (ISVLSI), 2012 IEEE Computer Society Annual Symposium on , vol.,no., pp.207,212, 19-21 Aug. 2012

- [10] G. K. Maity, J. N. Roy, and S.P. Maity, "Design of all-optical new gate using Mach-Zehnder interferometer", Devices, Circuits and Systems (ICDCS), 2012 International Conference on , vol., no., pp.474,478, 15- 16 March 2012

- [11] G. K. Maity and S.P. Maity, "Implementation of HNG using MZI", Computing Communication & Networking Technologies (ICCCNT), 2012 Third International Conference on , vol., no., pp.1,6, 26-28 July2012

- [12] Mehdi Saeedi and Igor L. Markov, "Synthesis and Optimization of Reversible Circuits A Survey", arXiv: 1110.2574v2 [cs.ET], 20 Mar 2013, pp. 1-34.

- [13] R. Feynman, "Quantum mechanical computers", Optical News, vol. 11, pp. 11-20 1985.

- [14] T. Toffoli, "Reversible computing", In Automata, Languages and Programming, Springer Verlag, pp. 632-644, 1980

- [15] T. Chattopadhyay, "All-optical modified fredkin gate," Selected Topics in Quantum Electronics, IEEE Journal of, vol. PP, no. 99, pp. 1 –8--2011.