A Peer Reviewed Open Access International Journal

### **Design of Efficient Shift Registers Using Pulsed Latches**

Shaik Reshma

L.Nageswara Rao, M.Tech (Ph.D)

M.Basha, M.Tech

M.Tech (VLSISD), Anurag Engineering College. Assistant Professor, Department of ECE, Anurag Engineering College. Associate Professor & HOD, Department of ECE,

Anurag Engineering College.

#### **Abstract:**

This paper proposes a low-control and area-proficient movement register utilizing computerized beat locks. The zone and power utilization are diminished by supplanting flip-flops with beat hooks. This technique takes care of the planning issue between beat locks using different non-cover postponed beat clock signals rather than the ordinary single beat clock signal. The movement register utilizes a little number of the beat clock signals by gathering the hooks to a few sub shifter registers and utilizing extra brief stockpiling locks. A 256-piece shift register utilizing beat hooks was manufactured utilizing a 0.18µm CMOS process with VDD = 1.8V. The center zone is  $6600\mu m^2$ . The force utilization is 1.2mW at a 100 MHz clock recurrence. The proposed shift register spares 37% territory and 44% force contrasted with the traditional movement register with flip-flops.

In advanced circuits, a movement register is a course of flip lemon, having the same clock, in which the yield of every flip-failure is associated with the "information" contribution of the following flip-flop in the chain, bringing about a circuit that movements by one position the "bit exhibit" put away in it, moving in the information present at its info and moving out the last piece in the cluster, at every move of the clock information. All the more for the most part, a movement register might be multidimensional, such that it's "information in" and stage yields are themselves bit clusters: this is actualized basically by running a few movement registers of the same piece length in parallel.

### **Keywords**:

Area-efficient, flip-flop, pulsed clock, pulsed latch, shift register.

#### I. Introduction:

Flip-flops are the fundamental stockpiling components utilized broadly as a part of a wide range of computerized outlines. As the element size of CMOS innovation process downsized by Law, creators can incorporate numerous quantities of transistors onto the same pass on. The more transistors there will be additionally exchanging and more power disseminated as warmth or radiation. Warmth is one of the wonder bundling challenges in this age, it is one of the primary difficulties of low power plan strategies and practices. Another driver of low power exploration is the dependability of the coordinated circuit. Additional exchanging infers higher normal current is removed and in this way the likelihood of unwavering quality issues happening rises. We are moving from portable workstations to tablets and significantly littler figuring advanced frameworks.

With this significant pattern proceeding and without a match drifting in battery future, the all the more low power issues will must be tended to. The present patterns will in the long run command low power outline computerization on an expansive scale to coordinate the patterns of force utilization of today's and future incorporated chips. Power] utilization of Very Large Scale Integrated outline is given by Generalized connection, P = CV2f [1]. Since force is corresponding to the square of the voltage according to the connection, voltage scaling is the most conspicuous approach to lessen power dissemination. Be that as it may, voltage scaling is results in limit voltage scaling which bows to the exponential increment in spillage power. In spite of the fact that few commitments have been made to the craft of single edge activated flip-tumbles, a need clearly

A Peer Reviewed Open Access International Journal

happens for an outline that further enhances the execution of single edge activated flip-flops designs. The design of a movement register is entirely basic. An N-bit shift register is made out of arrangement associated N information flip-flops. The velocity of the flip-failure is less essential than the range and power utilization in light of the fact that there is no circuit between flip-flips in the movement register. The littlest flip-lemon is reasonable for the movement register to lessen the territory and force utilization. As of late, beat hooks have supplanted flip-flops in numerous applications, on the grounds that a beat lock is much littler than a flip-flop. Be that as it may, the beat hook can't be utilized as a part of a movement register because of the planning issue between beat locks the hooks to a few sub shifter registers and utilizing extra impermanent stockpiling locks. Shift registers can have both parallel and serial inputs and yields.

### **II. Shift Registers:**

A movement register is the essential building hinder in a VLSI circuit. Shift registers are generally utilized as a part of numerous applications, for example, computerized channels, correspondence recipients and picture handling ICs Recently, as the extent of the picture information keeps on expanding because of the appeal for top notch picture information, the word length of the shifter register increments to process substantial picture information in picture preparing ICs.

A picture extraction and vector era VLSI chip utilizes a 4K-bit shift enroll A 10-bit 208 channel yield LCD segment driver IC utilizes a 2K-bit shift enlist A 16-megapixel CMOS picture sensor utilizes a 45K-piece shift register. As the word length of the shifter register builds, the territory and force utilization of the movement register get to be essential configuration contemplations. The littlest flip-failure is reasonable for the movement register to lessen the range and power utilization. As of late, beat locks have supplanted flip-flops in numerous applications, on the grounds that a beat hook is much littler than a flip-flop.

In any case, the beat hook can't be utilized as a part of a movement register because of the planning issue between beat locks.

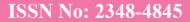

Figure 1: (a) Master-slave flip-flop. (b) Pulsed latch

This paper proposes a low-power and range proficient movement register utilizing beat hooks. The movement register takes care of the planning issue utilizing numerous non-cover postponed beat clock signals rather than the routine single beat clock signal. The movement register utilizes a little number of the beat clock signals by gathering These are regularly designed as 'serial-in, parallel-out' (SIPO) or as 'parallel-in, serial-out' (PISO). There are likewise sorts that have both serial and parallel information and sorts with serial and parallel yield. There are likewise "bidirectional" movement registers which permit moving in both bearings:

$L\rightarrow R$  or  $R\rightarrow L$ . The serial info and last yield of a movement register can likewise be associated with make a 'round movement register' past work regularly measured vitality utilization utilizing a restricted arrangement of information examples with the clock exchanging each cycle. Be that as it may, genuine outlines have a wide variety in clock and information action crosswise over various TE occasions. For instance, low power microchips make broad utilization of check gating bringing about numerous TEs whose vitality utilization is commanded by information moves as opposed to clock moves. Different TEs, conversely, have unimportant information action however are timed each cycle. Shift registers, similar to counters, are a type of consecutive rationale. Successive rationale, not at all like combinational rationale is influenced by the present inputs, as well as, by the earlier history.

A Peer Reviewed Open Access International Journal

As such, successive rationale recalls past occasions. Beat lock structures utilize an edge-activated heartbeat generator to give a short straightforwardness window. Contrasted with master—slave flip-flops, beat hooks have the upsides of requiring stand out lock stage per clock cycle and of permitting time-acquiring crosswise over cycle limits. The real weaknesses of beat lock structures are the expanded powerlessness to timing perils and the vitality dispersal of the nearby clock beat generators.

### **III. Proposed Architecture:**

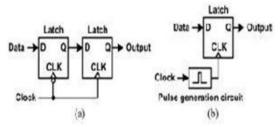

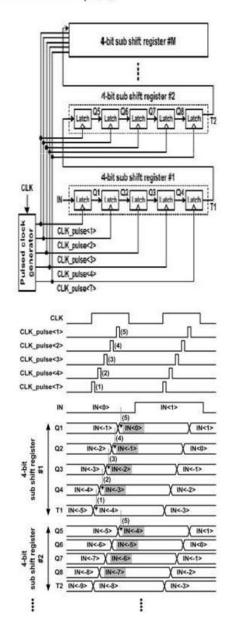

An expert slave flip-flop sing two locks in Fig.1 (a) can be supplanted by a beat hook comprising of a hook and a beat check signal in Fig. 1(b). All beat locks share the beat era circuit for the beat clock signal. Thus, the range and power utilization of the beat lock turn out to be half of those of the expert slave flip-flop. The beat lock is an appealing answer for little range and low power utilization. The beat hook can't be utilized as a part of movement registers because of the planning issue, as appeared in Fig. 2. The movement registers in Fig. 2(a) comprises of a few hooks and a beat clock signal (CLK pulse). The operation waveforms in Fig. 2(b) demonstrate the planning issue in the shifter registers. The yield sign of the primary lock (Q1) changes accurately in light of the fact that the information signs of the main hook (IN) are steady amid the clock beat width (TPULSE). Be that as it may, the second lock has an unverifiable yield signal (Q2) on the grounds that its info signal (Q1) changes amid the clock beat width.

Fig. 2. Shift register with latches and a pulsed clock signal. (a) Schematic. (b) Waveforms

One answer for the planning issue is to include delay circuits between hooks, as appeared in Fig. 3(a). The yield sign of the hook is deferred and achieves the following lock after the clock beat. As appeared in Fig. 3(b) the yield signs of the first and second hooks (Q1 and Q2) change amid the clock beat width, however the information signs of the second and third locks (D2 and D3) turn into the same as the yield signs of the first and second locks (Q1 and Q2) after the clock beat. Therefore, all locks have steady information signals amid the clock beat and no planning issue happens between the hooks. Nonetheless, the deferral circuits cause huge range and control over heads.

Fig. 3. Shift register with latches, delay circuits, and a pulsed clock signal. (a)Schematic. (b)Waveforms

A 4-bit sub shifter register comprises of five hooks and it performs shift operations with five non cover postponed beat clock signals (CLK\_pulse<1:4>and CLK\_pulse<T>). In the 4-bit sub shift register #1, four locks store 4-bit information (Q1-Q4) and the last latch stores 1-bit transitory information (T1) which will be put away in the principal lock (Q5) of the 4-bit sub shift register #2. Fig. 4(b) demonstrates the operation waveforms in the proposed shift enlist .The quantities of locks and clock-heartbeat circuit's change as indicated by the word length of the sub shift register is chosen by considering the territory, power utilization, speed.

#### **Power optimization:**

The force enhancement is like the range streamlining.

A Peer Reviewed Open Access International Journal

The force is devoured predominantly in locks and clock-beat circuits. Every lock expends power for information move and clock stacking.

Area optimization: The area optimization can be performed as follows. Whenthe circuit areas are normalized with a latch, the areas of a latchand a clock-pulse circuit are 1 and, respectively. The total area becomes  $(\alpha_A \times (K+1) + N(1+\frac{1}{\alpha})$ .

The optimal  $K = \sqrt{N/\alpha_A}$  for the minimum area is obtained from the first-order differential equation of the total area  $(0=\alpha_A-N/K)$ . An integer for the minimum area is selected as a divisor of, which is nearest to  $\sqrt{N/\alpha_A}$ .

# Fig. 4. Proposed shift register. (a) Schematic. (b) Waveforms

The quantities of locks and clock-heartbeat circuit's change as per the word length of the sub shift register is chosen by considering the range, power utilization, speed. Forces are standardized with a lock, the force utilization of a hook and a clock-beat circuit.

### **Chip Implementation:**

The most extreme check recurrence in the ordinary movement register is restricted to just the deferral of flip-failures in light of the fact that there is no postponement between flip-flips. In this way, the territory and force utilization are more critical than the velocity for selecting the flip-flop. The proposed shift register utilizes locks rather than flip-failures to diminish the zone and power utilization.

#### **IV. RESULTS**

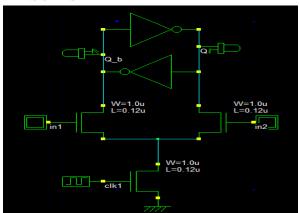

Fig. 5 Schematic of the SSASPL

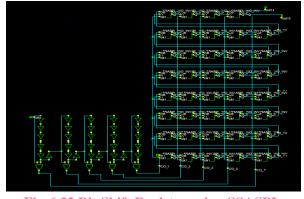

Fig:6 32 Bit Shift Register using SSASPL

A Peer Reviewed Open Access International Journal

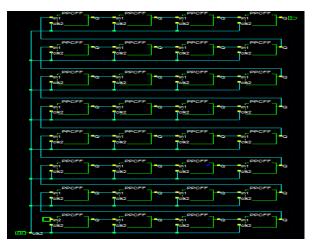

Fig: 7 32 Bit Shift Register using PPCFF

#### **COMPARISION ANALYSIS**

| PARAMETERS | PPCFF           | SSASPL         |

|------------|-----------------|----------------|

| 1. Area    | $31.41 \mu m^2$ | $8.42 \mu m^2$ |

| 2. Power   | 6.611 [mW]      | 2.876 [mW]     |

Table: 1Comparision of Area and Power of SSASPL and PPCFF

| PARAMETERS | PPCFF                  | SSASPL               |

|------------|------------------------|----------------------|

| 1. Area    | 60.25                  | 33.63µm <sup>2</sup> |

| 2. Power   | μm <sup>2</sup> 244.92 | 381.39 [mW]          |

|            | [mW]                   | 381.39               |

Table: 2Comparision of Area and Power of 16 bit Shift Register using SSASPL and PPCF

| PARAMETERS | PPCFF                     | SSASPL      |

|------------|---------------------------|-------------|

| 1. Area    | 90.926<br>μm <sup>2</sup> | 6.527µm²    |

| 2. Power   | 533.55<br>[mW]            | 313.61 [mW] |

Table: 3Comparision of Area and Power of 32 bit Shift Register using SSASPL and PPCFF

#### V. CONCLUSION:

This paper proposed a low-power and territory productive movement register utilizing beat hooks. The movement register diminishes region and force utilization by substituting flip-flops with beat hooks. The planning issue between beat locks is unraveled utilizing various non-cover postponed beat clock signals as an option of a solitary beat clock signal.

#### **REFERENCES:**

- [1]P. Reyes, P. Reviriego, J. A. Maestro, and O. Ruano, "New protection techniques against SEUs for moving average filters in a radiation environment," IEEE Trans. Nucl. Sci., vol. 54, no. 4, pp. 957–964, Aug. 2007.

- [2] M. Hatamianet al., "Design considerations for gigabit ethernet 1000 base-T twisted pair transceivers," Proc. IEEE Custom Integr. CircuitsConf., pp. 335–342, 1998.

- [3]H. Yamasaki and T. Shibata, "A real-time image-feature-extraction and vector-generation vlsi employing arrayed-shift-register architecture," IEEE J. Solid-State Circuits, vol. 42, no. 9, pp. 2046–2053, Sep. 2007.

- [4]H.-S. Kim, J.-H. Yang, S.-H. Park, S.-T. Ryu, and G.-H. Cho, "A 10-bit column-driver IC with parasitic-insensitive iterative charge-sharing based capacitor-string interpolation for mobile active-matrix LCDs," IEEE J. Solid-State Circuits, vol. 49, no. 3, pp. 766–782, Mar. 2014.

- [5] S.-H. W. Chiang and S. Kleinfelder, "Scaling and design of a 16-mega-pixel CMOS image sensor for electron microscopy," in Proc. IEEENucl. Sci. Symp. Conf. Record (NSS/MIC), 2009, pp. 1249– 1256.

- [6] S. Heo, R. Krashinsky, and K. Asanovic, "Activity-sensitive flip-flop and latch selection for reduced energy," IEEE Trans. Very Large ScaleIntegr.

A Peer Reviewed Open Access International Journal

- (VLSI) Syst., vol. 15, no. 9, pp. 1060–1064, Sep. 2007.

- [7] S. Naffziger and G. Hammond, "The implementation of the nextgen-eration 64 b itanium microprocessor," in IEEE Int. Solid-State CircuitsConf. (ISSCC) Dig. Tech. Papers, Feb. 2002, pp. 276–504.

- [8] H. Partoviet al., "Flow-through latch and edgetriggered flip-flop hy-brid elements," IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech.Papers, pp. 138–139, Feb. 1996.

- [9] E. Consoli, M. Alioto, G. Palumbo, and J. Rabaey, "Conditional push-pull pulsed latch with 726 fJops energy delay product in 65 nm CMOS," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech.Papers, Feb. 2012, pp. 482–483.

- [10] V. Stojanovic and V. Oklobdzija, "Comparative analysis of master-slave latches and flip-flops for high-performance and low-power sys-tems," IEEE J. Solid- State Circuits, vol. 34, no. 4, pp. 536–548, Apr. 1999.

- [11] J. Montanaroet al., "A 160-MHz, 32-b, 0.5-W CMOS RISC micropro-cessor," IEEE J. Solid-State Circuits, vol. 31, no. 11, pp. 1703–1714, Nov. 1996.

- [12] S. Nomura et al., "A 9.7 mW AAC-decoding, 620 mW H.264 720p 60fps decoding, 8-core media processor with embedded forward-body-biasing and power-gating circuit in 65 nm CMOS technology," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2008, pp. 262–264.

- [13] Y. Ueda et al., "6.33 mW MPEG audio decoding on a multimedia pro-cessor," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Pa-pers, Feb. 2006, pp. 1636–1637.

- [14] B.-S. Kong, S.-S. Kim, and Y.-H. Jun, "Conditional-capture flip-flop for statistical power reduction," IEEE J. Solid-State Circuits, vol. 36, pp. 1263–1271, Aug. 2001.

- [15] C. K. Teh, T. Fujita, H. Hara, and M. Hamada, "A 77% energy-saving 22-transistor singlephase-clocking D-flip-flop with adaptivecoupling configuration in 40 nm CMOS," in IEEE Int. Solid-State Circuits Conf.(ISSCC) Dig. Tech. Papers, Feb. 2011, pp. 338–339.