A Peer Reviewed Open Access International Journal

## A Single Phase Three Phase Seven-Level Switched-Capacitor Based Multilevel Inverter fed to Induction Motor Drive

### Peeta Lavanya

P.G. Scholar, Department of Electrical & Electronics Engineering, Chirala Engineering College, Chirala; Prakasam (Dt); A.P, India.

### V.Sivanagaraju

Assistant Professor, Department of Electrical & Electronics Engineering, Chirala Engineering College, Chirala; Prakasam (Dt); A.P, India.

#### Abstract:

By the conventional carrier based and space vector pulse width modulation (PWM) which schemes for two-level inverter topology generate large commonmode voltages, this leads to the phenomenon of bearing current. These current spikes can cause electromagnetic interference (EMI) and reduction in the life expectancy of the motor. Cascade multilevel inverters can reduce voltage stress on power switches; generate smaller common-mode voltages and output voltages with low disto rtion. Phase shifted PWM is a compatible solution for H-bridge cascaded inverters. This project proposes a novel single-phase seven-level inverter. The topology of the proposed structure is composed of a DC source, a switched-capacitor circuit, and a coupled inductor. Compared to conventional sevenlevel inverter structure, numbers of switches and capacitors are reduced. The voltages of capacitors are self-balanced by using coupled inductor without complex control method. the level- and phaseshifted PWM (LPS-PWM) and the LS-PWM are applied to the seven-level SCISPC, and LPS-PWM is compared with LS-PWM for the seven-lev el SCISPC. The LPS-PWM has both the chara cteristics of the phase-shifted PWM (PS-PWM) and the LS-PWM. The voltage reduction during the discharging term of the SCs is reduced by means of the shorter discharging period compared to LS-PWM. The voltage ripple of the capacitors is also reduced, which leads to higher power conversion efficiency. the improved seven level PWM conv erter version is also considered to suppress the circulating current due to phase shift pulse modulation principle by using MAT Lab/Simulink.

*Index Terms* — A boost converter, H-bridge, Switched capacitor converters, charge pump, switchedcapacitor, Induction Machine Drive.

### **1.INTRODUCTION**

The multilevel inverters have received a lot of attention because of high-efficiency power conversion. The output voltage of the multilevel inverter is in a staircase waveform. Therefore, the voltage stress of the switching device is lower, and the total harmonic distortion (THD) is also lower than that of the other types of inverter. The multilevel inverter has many configurations: for example, the cascade H-bridge (CHB) inverter [15]–[19], the neutral-point-clamped inverter [20], and the flying capacitor inverter. These inverters have a large number of switching devices or many input voltage sources. For example, the seven-level CHB has 12 switching devices [17]. As the voltage level increases, a greater number of switching devices are required.

A switched capacitor (SC) inverter, which outputs multilevel voltages with SCs, gives a solution against the multi-voltage-source structure. The SC inverter outputs a higher voltage than the input voltage in a similar way to the charge pump. However, the number of switching devices increases, which makes the circuit topology more complicated.

A simplified SC inverter, which is named the Marx inverter, is proposed. The Marx inverter has the less number of switching devices in the unique topology. A SC inverter using series/parallel conv ersion (SCISPC) is based on the Marx inverter structure and an Hbridge. The SCISPC can output a multilevel voltage waveform by switching the capacitors in series or in parallel. The SCISPC has the less number of switching devices compared to the conventional multilevel inverters.

Therefore, the SCISPC can be a solution against the aforementioned disadvantages. However, the efficiency of the SCISPC is reduced by the voltage reduction of the SCs when the conventional

A Peer Reviewed Open Access International Journal

multicarrier PWM is applied. There are many modulation methods to drive a multilevel inverter: the multicarrier PWM, the space vector modulation, the hybrid modulation [13], [37], [39], the selective harmonic elimination [13], [38], and the alternatively in opposition (APO) disposition PWM [40]. In the preliminary version of this paper [41], one of the APO PWMs is applied, which is the combination of the level-shifted PWM (LS-PWM) and the phase-shifted PWM (PS-PWM). That is called "level- and phaseshifted PWM (LPS-PWM)." The LPS-PWM realizes low voltage ripple on the capacitors in the SCISPC, which also leads to high-efficiency power conversion. In addition, the carrier frequency of LPS-PWM is reduced to half that of the conventional LS-PWM in SCISPC.

The modulation method, the determination method [11] of the capacitance, and the loss calculation of the inverter proposed. A charge pump outputs a larger voltage than the input voltage with switched capacitors [7], [8]. When the several capacitors and the input voltage sources are connected in parallel, the capacitors are charged. SC inverter is consists of a Marx inverter structure and an H-bridge [18]. The proposed inverter can output larger voltage than the input voltage by switching the capacitors in series and in parallel. The maximum output voltage is determined by the number of the capacitors.

The continuous economic development of many countries and the environmental issues (gas emissions and the green house effect) observed in the last decades forced an intense research in renewable energy sources. Hydro, photovoltaic (PV) and wind energy conversion are the most explored technologies due to their considerable advantages [1]-[2], such as reasonable installation reliability, and energy production costs, low environmental impact, capability to support micro-grid systems and to connect to the electric grid [3]. Among these energy sources the PV is pointed out as one of the most modular and environmentally friendly technologies. Therefore, PV systems have been frequently adopted worldwide, presenting a growth of 45% on the total PV power installed in 2009.

The proposed inverter does not have any inductors can be smaller than a conventional two-stage unit which consists of a boost converter and an inverter bridge, which make the system large. The structure of the inverter is simpler than [3] the conventional switchedcapacitor inverters. THD of the output waveform of the inverter is reduced compared to the conventional single phase full bridge inverter as the conventional multilevel inverter. In this paper, an SC inverter whose structure is simpler than the conventional SC inverter is proposed. It consists of a Marx inverter structure and an H-bridge. The proposed inverter can output larger voltage than the input [3] voltage by switching the capacitors in series and in parallel. The proposed inverter does not have any inductors which make the system large [4]. The output harmonics of the proposed inverter are reduced by the multilevel output.

### **CIRCUIT DESCRIPTION**

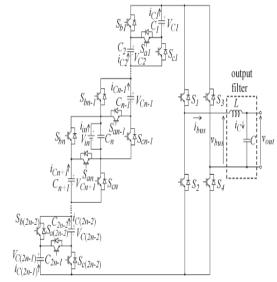

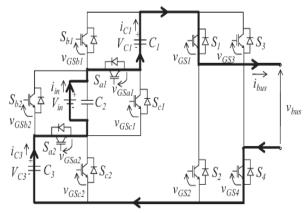

Fig. 1 shows a circuit topology of the proposed inverter, where *Sak*, *Sbk*, *Sck*(k = 1, 2, ..., 2n - 2) are the switching devices which switch the capacitors *Ck*(k = 1, 2, ..., 2n - 1) in series and in parallel. Switches *S*1 - *S*4 are in the inverter bridge.

# Fig.1. Circuit topology of the switched-capacitor inverter using series/parallel conversion

A voltage source Vin is the input voltage source. A lowpass filter is composed of an inductor L and a capacitor C. There are many modulation methods to drive a multilevel inverter: the space vector modulation the multicarrier pulse width modulation (PWM) the hybrid modulation the selective harmonic elimination and the nearest level control. In this paper,

A Peer Reviewed Open Access International Journal

the multicarrier PWM method is applied to the proposed inverter.

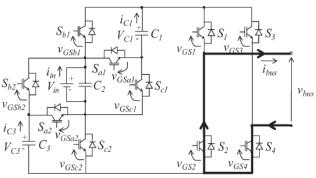

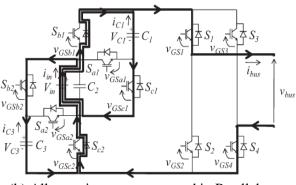

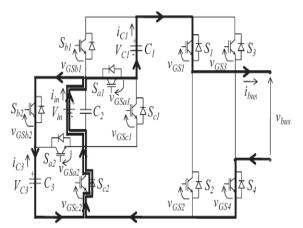

(a) The current *ibus* does not flow in the capacitors *Ck*,

(b) All capacitors are connected in Parallel

(c) The capacitor *C*1 is connected in series and the capacitor *C*3 is connected in parallel

(d) All capacitors are connected in series.Fig.2. Current flow of the proposed inverter (*n* = 2) on each state of (a),(b),(c)and(d)

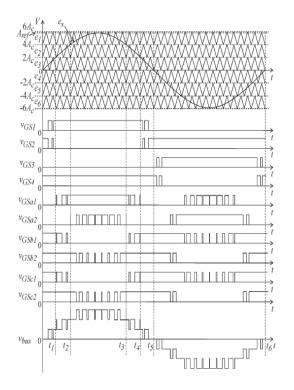

There are many modulation methods to drive a multilevel inverter: the space vector modulation the multicarrier pulse width modulation (PWM) the hybrid modulation the selective harmonic elimination and the nearest level control. In this paper, the multicarrier PWM method is applied to the proposed inverter. Fig. 2 shows the current flow in the proposed inverter (n = 2) and Fig. 3 shows the modulation method of the proposed inverter (n = 2). When the time *t* satisfies  $0 \le t < t1$  in Fig. 3, the switches S1 and S2 are driven by the gate-source voltage *vGS1* and *vGS2*, respectively. While the switches S1 and S2 are switched alternately, the other switches are maintained ON or OFF state as shown in Fig. 3.

Therefore, the states shown in Fig. 2(a) and (b) are switched alternately and the bus voltage Vbus takes 0 or Vin. When the time t satisfies  $t1 \le t < t2$  in Fig. 3, the switches Sa1, Sb1, and Sc1 are driven by the gatesource voltage vGSa1, vGSb1. and vGSc1. respectively. While the switches Sa1, Sb1, and Sc1 are switched alternately, the other switches are maintained ON or OFF state as shown in Fig.3.Therefore, the states shown in Fig. 2(b) and (c) are switched alternately. The capacitor C1 is charged by the current -iC1 as shown in Fig. 2(b) during the state shown in Fig.2(b). Therefore, the proposed inverter can output the bus voltage *vbus* while the capacitor C1 is charged. The bus voltage *vbus* in the state of Fig. 2(c) is

$$v_{bus} = V_{in} + V_{C1}$$

(1)

A Peer Reviewed Open Access International Journal

# MODULATION METHOD OF THE PROPOSED INVERTER

## Fig. 3. Modulation method of the proposed inverter (n = 2).

where VC1 is the voltage of the capacitor C1. Therefore, the proposed inverter outputs Vin or Vin + VC1 alternately in this term. When the time t satisfies  $t2 \le t < t3$  in Fig. 3, the switch Sa2, Sb2 and Sc2 are driven by the gate-source voltage vGSa2, vGSb2 and vGSc2, respectively. While the switches Sa2, Sb2, and Sc2 are switched alternately, the other switches are maintained ON or OFF state as shown in Fig. 3. Therefore, the states shown in Fig. 2(c) and (d) are switched alternately. The capacitor C3 is charged by the current -iC3 as shown in Fig. 2(c) during the state shown in Fig. 2(d) is

$$v_{bus} = V_{in} + V_{C1} + V_{C3}$$

(2) where VC3 is the voltage of the capacitor C3. Therefore, the proposed inverter outputs Vin + VC1 or Vin + VC1 + VC3 alternately in this term. After t = t3, the four states shown in Fig. 2 are repeated by turns. Table I shows the list of the on-state switches when the proposed inverter (n = 2) is driven by the modulation method shown in Fig. 3. The ideal bus voltage *vbus* in Table I means the bus voltage on each state when VC1 = VC3 = Vin is assumed.

As the conventional SC inverter, the proposed inverter has a full bridge which is connected to the high voltage.

TABLE I LIST OF THE ON-STATE SWITCHES ON EACH STATE

| Relationship between $e_s$ and $e_k$ | On-state switches                          | Ideal bus voltage $v_{bus}$ |

|--------------------------------------|--------------------------------------------|-----------------------------|

| $e_{s} > e_{1}$                      | $S_1, S_4, S_{a1}, S_{a2}$                 | $3V_{in}$                   |

| $e_1 \ge e_s > e_2$                  | $S_1, S_4, S_{a1}, S_{b2}, S_{c2}$         | $2V_{in}$                   |

| $e_2 \ge e_s > e_3$                  | $S_1, S_4, S_{b1}, S_{c1}, S_{b2}, S_{c2}$ | $V_{in}$                    |

| $e_3 \ge e_s > e_4$                  | $S_2, S_4, S_{b1}, S_{c1}, S_{b2}, S_{c2}$ | 0                           |

| $e_4 \ge e_s > e_5$                  | $S_2, S_3, S_{b1}, S_{c1}, S_{b2}, S_{c2}$ | $-V_{in}$                   |

| $e_5 \ge e_s > e_6$                  | $S_2, S_3, S_{b1}, S_{c1}, S_{a2}$         | $-2V_{in}$                  |

| $e_6 \ge e_s$                        | $S_2, S_3, S_{a1}, S_{a2}$                 | $-3V_{in}$                  |

Therefore, the device stress of the switches S1 - S4 in the full bridge is higher than the other switches as the conventional SC inverter. The proposed inverter (n = 2) outputs a 7-level voltage by repeating the four states as shown in Fig. 2. Because the driving waveform vGSa1 and vGSa2 change alternately as shown in Fig. 3, the capacitors C1 and C3 are equally discharged. Assuming that the number of the capacitors is 2n - 1, the proposed inverter can outputs 4n - 1 levels voltage waveform. The modulation index M is defined as the following equation because the amplitude of the output voltage waveform is inversely proportional to the double amplitude of the carrier waveform.

$$M = A_{ref}/2A_c.$$

In (3), *Aref* is the amplitude of the reference waveform and *Ac* is the amplitude of the carrier waveform. The proposed inverter requires 10 switching devices for the 7-level, and 16 switching devices for the 11-level. On the other hand, the conventional SC inverter requires 20 switching devices for the 7-level, and 28 switching devices for the 11-level [9]. The conventional cascaded H-bridge (CHB) inverter requires 12 switching devices for the 7-level, and 20 switching devices for the 11-level, when all the dc voltage sources take the same voltage [17]. Therefore, the proposed inverter has less number of switching devices than the conventional multilevel inverters.

(3)

A Peer Reviewed Open Access International Journal

## DYNAMIC MODELLING OF INDUCTION MOTOR

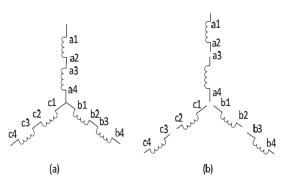

In a conventional four pole induction motor, there are two sets of identical voltage profile windings will be present in the total phase winding. These two windings are connected in series as shown in fig. 4(a). For the proposed inverter these two identical voltage profile winding coils are disconnected, and the available four terminals are taken out, like shown in the fig.4 (b). Since these two windings are separated equally, stator resistance, Stator leakage inductance and the magnetizing inductance of each identical voltage profile windings are equal to the half of the normal induction motor shown in fig.4 (a). The voltage equitation for the stator winding is given by common dc link.

$$V_{a1} - V_{a2} = \left(\frac{r_s}{2}\right) * i_{as} + \left(\frac{L_{ss}}{2}\right) * i_{as} - \left(\frac{1}{2}\right) * \left(\frac{L_m}{2}\right) * i_{bs} - \left(\frac{1}{2}\right) * \left(\frac{L_m}{2}\right) * i_{cs}$$

$$V_{a3} - V_{a4} = \left(\frac{r_s}{2}\right) * i_{as} + \left(\frac{L_{ss}}{2}\right) * i_{as} - \left(\frac{1}{2}\right) * \left(\frac{L_m}{2}\right) * i_{bs}$$

(4)

$$\begin{array}{c} \begin{array}{c} & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & & \\ & & & \\ & & & \\ & & & & \\ & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & \\$$

Fig. 4 Induction Motor stator winding: (a) General arrangement (b) Arrangement for the proposed inverter

The effective voltage across the stator winding is the sum of the voltages across the two individual windings.

$$V_{as} = (V_{a1} - V_{a2}) + (V_{a3} - V_{a4})$$

(6)

The motor phase voltage can be achieved by substituting equations (4) and (5) in (6)

$$V_{as} = r_s * i_{as} + L_{ss} * i_{as} - \left(\frac{1}{2}\right) * L_m * i_{bs} - \left(\frac{1}{2}\right) * L_m * i_{cs}$$

<sup>(7)</sup>

Similarly voltage equitation for the remaining phases are

$$V_{bs} = r_s * i_{bs} + L_{ss} * i_{bs} - \left(\frac{1}{2}\right) * L_m * i_{as} - \left(\frac{1}{2}\right) * L_m * i_{cs}$$

(8)

$$V_{cs} = r_s * i_{cs} + L_{ss} * i_{cs} - \left(\frac{1}{2}\right) * L_m * i_{as} - \left(\frac{1}{2}\right) * L_m * i_{bs}$$

(9)

Voltage equations in dq0 frame can be solved from the basic equations of induction motor

$$\begin{split} V_{qs} &= r_s * i_{qs} + \omega * \lambda_{ds} + \rho * \lambda_{qs} \\ V_{ds} &= r_s * i_{ds} - \omega * \lambda_{qs} + \rho * \lambda_{ds} \\ V_{0s} &= r_s * i_{0s} + \rho * \lambda_{0s} \\ V_{qr} &= r_r * i_{qr} + (\omega - \omega_r) * \lambda_{dr} + \rho * \lambda_{qr} \\ V_{dr} &= r_r * i_{dr} - (\omega - \omega_r) * \lambda_{qr} + \rho * \lambda_{dr} \\ V_{0r} &= r_r * i_{0r} + \rho * \lambda_{0r} \end{split}$$

Flux linkages are as follows

$$\lambda_{qs} = L_{ss} * i_{qs} + L_M * i_{qr}$$

$$\lambda_{ds} = L_{ss} * i_{ds} + L_M * i_{dr}$$

$$\lambda_{0s} = L_{1s} * i_{0s}$$

$$\lambda_{qr} = L_{rr} * i_{qr} + L_M * i_{qs}$$

$$\lambda_{dr} = L_{rr} * i_{dr} + L_M * i_{ds}$$

$$\lambda_{0r} = L_{1r} * i_{0r}$$

The expression for the electromagnetic torque in terms of dq0 axis currents is

$$T_{e} = \left(\frac{3}{2}\right) * \left(\frac{P}{2}\right) * L_{M} * \left(i_{qs} * i_{dr} + i_{ds} * i_{qr}\right)$$

(10)

Rotor speed in terms of Torque is

$$\frac{\mathrm{d}}{\mathrm{d}t}\omega_{\mathrm{e}} = \left(\frac{\mathrm{P}}{2*\mathrm{J}}\right)*\left(T_{e}-T_{L}\right) \tag{11}$$

Where

d: direct axis, q: quadrature axis, s: stator variable,

A Peer Reviewed Open Access International Journal

r: rotor variable,

$V_{ds}, V_{qs}$ ,: q and d-axis stator voltages,  $V_{dr}, V_{qr}$ ,: q and d-axis rotor voltages,  $r_r$ : Rotor resistance,  $Vr_s$ : Stator resistance, L1s: stator leakage inductance, L1r: rotor leakage inductance, iqs, ids: q and d-axis stator currents, iqr, idr: q and d-axis rotor currents, p: number of poles, J: moment of inertia, Te : electrical output torque, TL : load torque.

From the equations (4), (5),(6) it can be observed that there is no difference between the normal induction motor shown in fig.2 (a) and the disconnected (Identical voltage profile windings) motor shown in fig.2 (b).

### SIMULATION RESULTS

Here simulation is carried out in different cases 1). Proposed Single Phase Series/Parallel Topology 2). Proposed Three Phase Series/Parallel Topology Applied to Induction machine Drive.

Case 1: Proposed Single Phase Series/Parallel Topology

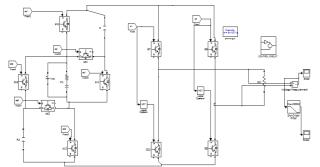

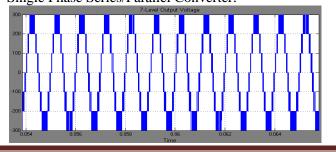

Fig. 5 Matlab/Simulink Model of Proposed Single Phase Series/Parallel Converter Fig.5 shows the Matlab/Simulink Model of Proposed Single Phase Series/Parallel Converter.

Fig. 6 Seven Level Output Voltage

As Fig.6 shows the single phase seven level output voltage without filter of proposed series/parallel converter.

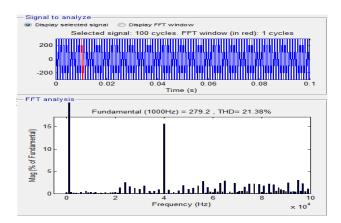

Fig. 8 FFT Analysis of Output Voltage without Filter of Proposed Series/Parallel Converter

As above Fig. 8 shows the FFT Analysis of Output Voltage without Filter of Proposed Series/Parallel Converter, we get 21.38%.

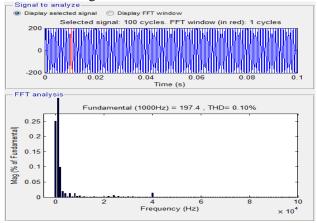

As above Fig. 9 shows the FFT Analysis of Output Voltage with Filter of Proposed Series/Parallel Converter, we get 0.10%.

Case 2: Proposed Three Phase Series/Parallel Topology Applied to Induction machine Drive.

Volume No: 2 (2015), Issue No: 12 (December) www.ijmetmr.com

December 2015

A Peer Reviewed Open Access International Journal

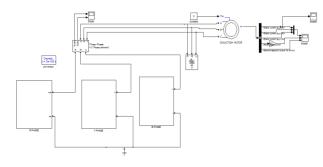

Fig. 10 Matlab/Simulink Model of Proposed Three Phase Series/Parallel Converter Applied to IM Drive

Fig.10 shows the Matlab/Simulink Model of Proposed Three Phase Series/Parallel Topology Applied to Induction machine Drive.

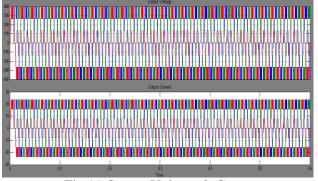

Fig.11 Output Voltage & Current

Fig.11 shows the Output Voltage & Current of Proposed Three Phase Series/Parallel Topology.

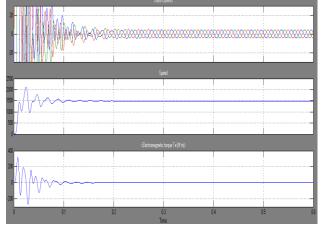

Fig.12 Stator Currents, Speed, Electromagnetic Torque Fig.12 Stator Currents, Speed, Electromagnetic Torque of Proposed Three Phase Series/Parallel Topology Applied to Induction machine Drive.

### CONCLUSION

With the advancement of power electronics and emergence of new multilevel converter topologies, it is possible to work at voltage levels beyond the classic semiconductor limits. The multilevel converters achieve high-voltage switching by means of a series of voltage steps, each of which lies within the ratings of the individual power devices. In this paper, a novel boost switched-capacitor inverter was proposed & proposed three phase series/parallel topology applied to induction machine drive to check the performance of drive characteristics, the circuit topology was introduced. The modulation method, the determination method of the capacitance, and the loss calculation of the proposed inverter were shown. The circuit operation of the proposed inverter was confirmed by the simulation results with a resistive load and a machine load. The proposed inverter outputs a larger voltage than the input voltage by switching the capacitors in series and in parallel. The structure of the inverter is simpler than the conventional switchedcapacitor inverters. THD of the output waveform of the inverter is reduced compared to the conventional single phase full bridge inverter as the conventional multilevel inverter.

#### REFERENCES

[1] J. I. Rodriguez and S. B. Leeb, "A multilevel inverter topology for inductively coupled power transfer," *IEEE Trans. Power Electron.*, vol. 21, no. 6, pp. 1607–1617, Nov. 2006.

[2] X. Kou, K. A. Corzine, and Y. L. Familiant, "A unique fault-tolerant design for flying capacitor multilevel inverter," *IEEE Trans. Power Electron.*, vol. 19, no. 4, pp. 979–987, Jul. 2004.

[3] L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, and

M. A. M. Prats, "The age of multilevel converters arrives," *IEEE Ind. Electron. Mag.*, vol. 2, no. 2, pp. 28–39, Jun. 2008.

[4] Y. Hinago and H. Koizumi, "A single phase multilevel inverter using

switched series/parallel DC voltage sources," *IEEE Trans. Ind. Electron.*,vol. 57, no. 8, pp. 2643–2650, Aug. 2010.

[5] K.N.V Prasad, G.Ranjith Kumar, T. Vamsee Kiran, G.Satyanarayana., "Comparison of different topologies of cascaded H-Bridge multilevel inverter," Computer Communication and Informatics (ICCCI), 2013

A Peer Reviewed Open Access International Journal

International Conference on , vol., no., pp.1,6, 4-6 Jan. 2013.

[6] R. Gupta, A.Ghosh, and A. oshi, "Switching characterization of cascaded multilevel-inverter-controlled systems," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 1047–1058, Mar. 2008.

[7] J. Zhang, Y. Zou, X. Zhang, and K. Ding, "Study on a modified multilevel cascade inverter with hybrid modulation," in *Proc. IEEE Power Electron. Drive Syst.*, Oct. 2001, pp. 379–383.

[8] V. G. Agelidis, A. I. Balouktsis, and C. Cossar, "On attaining the multiple solutions of selective harmonic elimination PWM three-level waveforms through function minimization," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 996–1004, Mar. 2008.

[9] O. C.Mak and A. Ioinovici, "Switched-capacitor inverter with high power density and enhanced regulation capability," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 45, no. 4, pp. 336–347, Apr. 1998. [10] B. Axelrod, Y. Berkovich, and A. Ioinovici,"A cascade boost-switchedcapacitor- converter-two level inverter with an optimized multilevel output waveform," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 52, no. 12, pp. 2763–2770, Dec. 2005.

[11] S. Lu, K. A. Corzine, and M. Ferdowsi, "A unique ultracapacitor direct integration scheme in multilevel motor drives for large vehicle propulsion," *IEEE Trans. Veh. Technol.*, vol. 56, no. 4, pp. 1506–1515, Jul. 2007.

[12] J. I. Leon, S. Vazquez, A. J. Watson, L. G. Franquelo, P. W. Wheeler, and J. M. Carrasco, "Feed-forward space vector modulation for single-phase multilevel cascaded converters with any dc voltage ratio," *IEEE Trans. Ind. Electron.*, vol. 56, no. 2, pp. 315–325, Feb. 2009.