A Peer Reviewed Open Access International Journal

# High Performance and Area Delay Efficient Interpolation Filter Architecture

Ankita Anshu M.Tech (VLSI), CMR Institute of Technology, Hyderabad, India. B.S.Priyanka Kumari Assistant Professor, CMR Institute of Technology, Hyderabad, India. Surya Kumari Assistant Professor,

CMR Institute of Technology, Hyderabad, India.

#### Abstract

Finite Impulse Response (FIR) filters area unit wide applied in multi-standard wireless communications.

These filters supply linear section and absolute stability. The FIR offers a low sensitivity for the constant quantization errors. These properties increase the usage of FIR filter. Throughout this paper, reconfigurable interpolation filter architecture is projected. The approach is compatible if the filter order is mounted. The filter is self-propellingly reconfigured by dynamical the filter order. The order is changed by turning of the multiplier whose inputs area unit mitigates to be eliminated. The complexity of linear section FIR filters is dominated by the amount of adders (sub-tractors) among the constant number. The conventional multiplier is replaced by Dadda multiplier which reduces delay and dynamically reconfigurable filters are going to be efficiently enforced.

Index Terms—Approximate filtering, low power filter, reconfigurabledesign, Dadda Multiplier.

#### I. INTRODUCTION

Software radios will considerably scale back the value and quality of today's cellular radio base stations. software system radios architectures centre on the employment of wide band (WB) A/D converters and D/A converters as near the antenna as potential, with the maximum amount radio practicality as potential enforced within the digital domain. The reconfigurable FIR filters area unit wide employed in multiband mobile communication system. The filters exploitation in mobile communication system should be operative in low frequency and understand to consumes less power and high speed. The advance technologies in mobile communication systems area unit hard-to-please the low power and low quality techniques. The software system outlined Radio (SDR) and also the FIR filter researches area unit centered on reconfigurable realizations [2]. The SDR technology accustomed replace the analog signal process with digital signal process so as to supply versatile reconfiguration. A SDR style should meet today's reconfigurability necessities and adapt to rising standards, still as accommodate value, power and performance demands. Reconfigurability of the receiver to figure with totally different wireless communication standards is Associate in Nursingother key demand in an SDR. typically the quality of FIR filter depends upon the quantity of adders performs within the number unit.

Chanalizer is understood because the most significant block of the SDR that operates in high sampling rate however the SDR should be realizing of low power consumption and high speed. employing a bank of FIR filters within the channel filters introduces the multiple numbers of narrowband channels from a band signal.

Software created public radio (SDR) is one altogether the foremost necessary topics of study, then development, within the house of mobile and private communications. SDR is viewed as Associate in Nursing enabler of worldwide roaming and as a singular platform for the short introduction of recent services into existing live networks. It thus guarantees mobile communication networks an enormous increase in flexibility and capability [1]. SDR is formed public as a radio within that the receive conversion is performed at some stage downstream from the antenna, usually once broadband filtering, low noise amplification, and down conversion

Volume No: 4 (2017), Issue No: 2 (February) www.ijmetmr.com

A Peer Reviewed Open Access International Journal

to a lower frequency in ulterior stages- with a reverse methodology occurring for the transmit conversion. methodology Digital signal in versatile and reconfigurable useful blocks defines the characteristics of the radio [2].Design of SDR systems hard as a results of it's extremely tough to vogue a system that preserves most of ties of the proper package radio whereas being realizable with current-day technology. The chances to vogue package radio architectures vary from "Velcro" approach to a "Very Fine Grain" approach [3]. The "Velcro" approach aims to support many communication commonplaces through a number of self-contained tough communication components; every completely dedicated to a given traditional. On the contrary, "Very Fine Grain" approach depends on manipulating little size operators/components to support completely utterly totally different standards.

#### **II. LITERATURE REVIEW**

The computer approach may be a easy approach and thence comparatively easy. however the most downside is that, the number of branches of filtering-DDC-SRC is directly proportional to the amount of received channels i,e. The quality of the computer approach is directly proportional to the amount of channels. Thence the computer approach isn't economical once the number of received channels is giant. The filters utilized in the computer approach are of a awfully high order and this ends up in high space quality and so enhanced static power. DFTFBs cannot extract channels with totally different bandwidths referred to as heterogeneous channels, as a result of } modulated FBs with equal information measure for all band pass filters-the bandwidths are same as that of the epitome LPF. Therefore, for multi-mode receivers, distinct DFTFBs are needed for every communication commonplace.

Thence the quality the channelizer will increase linearly with the amount of standards. If the channel information measure is incredibly little compared with broadband signal (extremely narrowband channels), the epitome filter should be highly selective leading to a awfully high-order filter. As the order of the filter will increase,

the quality will increase linearly. Additionally the DFT size has to be enhanced. Pucker, L. in paper [2] entitled -Channelization techniques for software package outlined radio planned DFT Filter Banks. DFT filter bank may be a uniformly modulated filter bank, that has been developed as associate degree economical substitute for computer approach once the amount of channels have to be compelled to be extracted is additional, and also the channels ar of uniform information measure (for example several single commonplace communication channels have to be compelled to be extracted). the most advantage of DFT filter bank is that, it will expeditiously utilize the polyphonic letter decomposition of filters. the constraints of DFTFBs ar that the channel filters have fastened equal bandwidths equivalent to thespecification of a given standard's. Mahesh et.al. in paper [3] entitled -Reconfigurable Low space quality Filter Bank design supported Frequency Response Masking for Non uniform canalisation in software package Radio Receivers planned a replacement reconfigurable FB supported the FRM approach for extracting multiple channels of non-uniform bandwidths.

The FRM approach is changed to attain following advantages: 1) incorporate reconfigurability at the filter level and field of study level, 2) improve the speed of filtering operation, and 3) scale back the quality.

#### **III. FIR FILTER WITH MULTIPLIER BLOCK**

Figure-1 shows 3 full-parallel, fixed-coefficient FIR filter structures that square measure mathematically identical however disagree in design. Derived from the quality FIR structure using cut-set retiming, the backward FIR yields a uniform mathematical response however with many benefits for FPGA implementation: 1. No input sample shift registers square measure needed since every sample is fed to every faucet at the same time 2. The pipelined addition chain maps with efficiency 3. Filter latency is reduced4. Identical faucet constant magnitudes will sharemultiplication hardware as a result of faucets receives the input sample at the same time.

A Peer Reviewed Open Access International Journal

Fig1: Block Diagram of Minimized AdderGraph

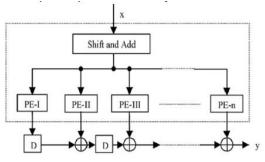

Fig2. Transposed direct form of an FIR filter

### **IV.PROPOSED FILTER ARCHITECTURES**

Co-efficient Selection Unit

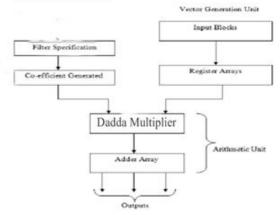

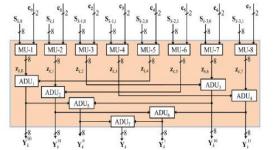

Fig.3: Architecture of the proposed method

#### **Coefficient selection unit:**

The CSU is comprised of number of J :1MUXes or N number of ROM LUTs of depth words each, where is the filter length and is the number of interpolation filters of different coefficient vector to be realized in the reconfigurable architecture. To avoid longer critical path delay, MUX-based CSU is used.

#### Input-vector generation unit (VGU):

The VGU receives one input-block in each cycle and generates input-vectors of size each in parallel, where is the smallest up-sampling factor from a set of different up-sampling factors to be realized by the reconfigurable architecture.

Fig4: Internal structure of the vector generation unit (VGU) for a set of up-sampling factors

### Arithmetic-unit

Fig5: Structure of the arithmetic unit (AU) for a set of up-sampling factors

#### **V. RESULTS & SIMULATION**

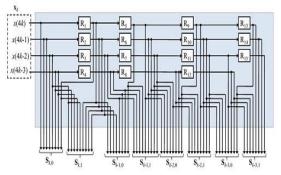

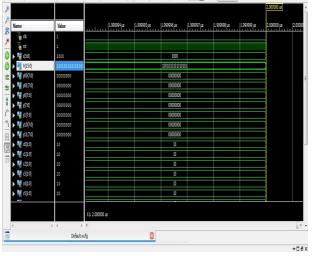

The written Verilog HDL modules have successfully simulated and verified using Isim simulator and synthesized in Xilinx14.1.

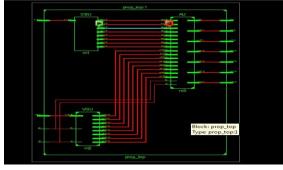

Fig 6: RTL Schematic

February 2017

A Peer Reviewed Open Access International Journal

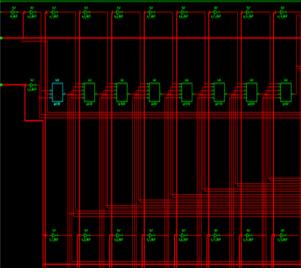

Fig 7: Technology Schematic

Fig.8:16-Bit Efficient Interpolation Filter

#### **VI.CONCLUSION**

A new approach to design an Efficient modified reconfigurable interpolation filter improves the speed. The proposed configurable filters architecture results in low delay which will give more efficient performance for SDR applications.

The 16bit efficient interpolation filter architecture using conventional multiplier has 19.715ns delay and after using Daddamultipler delay is reduced to 18.749ns. This type of Multiplier-less deigns are the best choice in many wireless system application.

#### REFERENCES

[1] T. Hentschel and G. Fettweis, "Software radio receivers," in CDMA Techniques for Third Generation Mobile Systems, Dordrecht, The Netherlands: Kluwer Academic,1999,pp.257–83

[2] J. Mitola, "Object-oriented approaches to wireless systemsengineering," in Software Radio Architecture. NewYork:Wiley,2000.

[3] Muhammad, Khurram and Roy, Kaushik, "A

Computational Redundancy Reduction Approach for

Highperformance and Low Power DSP

AlgorithmImplementation" (1999). ECE Technical

Reports Paper 36

[4] B. Parhami, "Implementation details," in ComputerArithmetic. New York: Oxford Press, 2000, p. 131.

[5] X.-J. Zhang, K.-W. Ng, and W. Luk, "A combined approach to high level synthesis for dynamically reconfigurable systems," in Proc. 10th Int. Workshop Field Programmable Logic Applicat., 2000, pp. 361–370

[6] R. Mahesh, Member, IEEE, and A. P. Vinod, SeniorMember, IEEE "New Reconfigurable Architectures forImplementing FIR Filters with Low Complexity" IEEEtransactions on computer-aided designofintegratedcircuits.

and systems, vol. 29, no. 2, February 2010.

[7] B.Ramkumar, Harish M Kittur, P.Mahesh Kannan" ASIC Implementation of Modified Faster Carry Save Adder"European Journal of Scientific Research ISSN 1450-216XVol.42 No.1 (2010), pp.53-58

[8] K.N. Macpherson and R.W. Stewart" Area efficient FIRfilters for high speed FPGA Implementation" RAPIDPROTOTYPING,Dec2006.

[9] M. M. Peiro, E. I. Boemo, and L. Wanhammar, "Design of high-speed multiplier less filters using a non

A Peer Reviewed Open Access International Journal

recursive signed common sub expression algorithm," IEEE Trans.Circuits Syst. II , vol. 49, no. 3, pp. 196203,Mar.2002.

[10] R. Mahesh and A. P. Vinod, "A new common subexpression elimination algorithm for realizing lowcomplexity higher order digital filters," IEEE Trans.Computer Aided Design Integrated Circuits Syst., vol. 27,no. 2, pp.217–219, Feb. 2008.

Volume No: 4 (2017), Issue No: 2 (February) www.ijmetmr.com