### International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

### Low Power Low Area Efficient Carry Select Adder

### **Gouda Venugopal**

M.Tech,

Jyothishmathi Institute of science &

Technology, karimnagar,

Telangana.

### K.Radhika Reddy

M.Tech,

Jyothishmathi Institute of science &

Technology, karimnagar,

Telangana.

### D.Ravi Kiran Babu, M.Tech

HOD,

Dept of ECE,

Jyothishmathi Institute of science &

Technology, karimnagar,

Telangana.

### I. INTRODUCTION:

Adders have a special significance in VLSI designs and it is used in computer and many other processors. It is used to calculate addresses, table indices and similar applications. Adders are also used in multipliers, in high speed integrated circuits and in digital signal processing. Now a days design of low power and area efficient high speed data path logic systems are most substantial area in the research of VLSI design. Number of fast adders can be used for addition. In digital adders the sum of each bit position is added and the generated carry is propagated into the next position. The propagated carry reduces the speed of addition. The carry select adder can be used to alleviate this problem. Carry select adder is one of thefastest adders having less area and powerconsumption. Itgenerates partial sum and carry by considering carry input Cin=0 and Cin=1, the final sum and carry are selected by the multiplexers. The main idea used in this project is to useBinary to Excess- 1 convertor(BEC) instead of RCA to reduce the area. This paper is organized in the following sections. II. Literature surveyIIIBEC.IV Explanation about regular SQRT CSLA and modified SQRT CSLAV.ResultVI Conclusion.

### **II. LITERATURE SURVEY:**

There are different types of fast adders used in processors such as ripple carry adder(RCA), carry look aheadadder (CLA) and carry select adder. Ripple carry adder provides compact design but their computation time is high. Carry look ahead adder gives fast result but it leads to an increase in area. Carry select adder provides a compromise between RCA and carry look ahead adder. Ripple carry adder produces worst case delay, because it consists of N single bit full adders. Each adderproduces the sum and carry. The carry of the previous full adder is given as the input to the next adder.

The carry is transferred through every stage and produces a delaycalled worst case delay. In ripple carry adder as value of N increases, delay also increases. So ripple carry adder has the lowest speed among the fast adders. The CSLA is used to anticipate all possible values of input carry i.e. o and 1 and evaluates the result in advance. The result is selected by the multiplexer. The CSLA uses dual RCA's to generate partial sum and carry by considering Cin=0 and Cin=1 then the final sum and carry is selected by using multiplier. In regular CSLA area consumed is more due to the use of dual RCA's. The basic idea of this work is to use Binary to excess-1 convertor(BEC) instead of RCA with Cin=1to reduce the area and power. The advantage of BEC is that it uses less number of logic gates than N bit full adders. To reduce thedelay N bit ripple carry adders are replaced with N+1 bit BEC .So modified SQRT CSLA is area consuming than regular CSLA.

### III .CSLA with BEC:

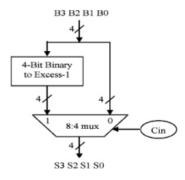

Modified CSLA uses BEC.BEC is a circuit used to add 1 to input numbers. The circuit of 4 bit BEC is shown in figure 1 and the truth table is shown in table 1.

Fig1. 4 bit Binary to Excess-1 Convertor

BEC consist of 4 inputs and the result is obtained by adding 1 with each of it. The expressions of 4 bit BEC are listed below.

## International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

X0=~B0 X1=B0^B1 X2=B2^(B0&B1) X3=B3^(B0&B1&B2)

#### TABLE1 TRUTH TABLE OF 4 BITS BINARY TO EXCESS -1 CONVERTOR

| CONTRACTOR    |  |

|---------------|--|

| Excess-llogic |  |

| X0,X1,X2,X3   |  |

| 0001          |  |

| 0010          |  |

| 0011          |  |

| 0100          |  |

| 0101          |  |

| 0110          |  |

| 0111          |  |

| 1000          |  |

| 1001          |  |

| 1010          |  |

| 1011          |  |

| 1100          |  |

| 1101          |  |

| 1110          |  |

| 1111          |  |

| 0000          |  |

|               |  |

Fig2. 4 Bit Binary to excess-1 logic with 8:4 multiplexer Addition is achieved using BEC together with multiplexer as shown in figure 2 .If the select line of MUX is 0 then input is (B3,B2,B1 and B0) otherwise input is BECs output.

Fig3.Block diagram of modified carry select adder

Thus modified CSLA is designed such that it occupies less area and low power than regular CSLA. Also RCAis replaced with BEC.

# IV.DELAY AND AREA OF REGULAR 16 BIT ADDER:

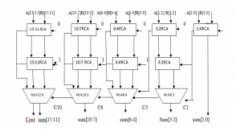

The delay can be calculated by adding up the number of gates in the longest path of logic block that contributes maximum delay. The area evolution is done by counting the total number of AOI gates required for each logic block. The structure of 16 bit regular SQRT CSLA is shown in fig 4, Proposed design has five groups of different size RCA. Each group contain dual RCA and MUX. The delay and area of each group is calculated and at last finds the total area and delay. The main disadvantage of regular CSLA is high area usage that can be overcome by using modified CSLA.

Fig4. Regular 16 bit SQRT CSLA

Modified SQRT CSLA is similar to that of regular SQRT CSLA the only difference we replace RCA with Cin=1 with BEC. The replaced BEC perform the same operation as that of the replaced RCA with C in=1. Figure 5 shows the modified SQTR CSLA. This structure consumes less area, delay and power than regular SQRT CSLA.

Fig5. Modified 16 bit SQRT CSLA

### **V.RESULT:**

This work is developed using Xilinx tool. Table II shows the comparison between different adders like regular SQRT CSLA, modified SQRT CSLA etc. The parameters compared are area and power. Modified SQRT CSLA has lesser number of logic gates and hence less area.

### International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

TABLE.IICOMPARISON OF ADDERS FOR AREA, DELAY.POWER

| Adder                              | Area<br>(No. of<br>gate<br>count) | Delay(ns) | Power(Mw) |

|------------------------------------|-----------------------------------|-----------|-----------|

| Conventional<br>(Dual RCA)         | 480                               | 19.81     | 94.63     |

| Modified( with BEC)                | 381                               | 21.59     | 81.38     |

| Regular SQRT<br>(with dual<br>RCA) | 348                               | 16.15     | 315       |

| Modified<br>SQRT(with<br>BEC)      | 291                               | 18.77     | 268       |

### **VI.CONCLUSION:**

In VLSI design process power, delay and area are the important factors that determine the performance of any circuit. This work is to reduce the area, power and delay of CSLA.

The regular CSLA has the disadvantage of more power consumption and large area. So modified CSLA overcomes this .It reduces the area and power which make it simple and efficient for VLSI hardware implementation

#### **REFERENCES:**

- [1] B.Ramkumar and Harish M kittur —low power and area –efficient carry select adder February 2013.

- [2] Kuldeep Rawat, Tarek Darwish and magdy Bayoumi A low power and reduced area carry select adder.

- [3] Y.kim and L.S Kim 64-bit carry select adder with reduced area.

- [4] O. J. Bedrij, —Carry-select adder,

- [5] T. Y. Ceiang and M. J. Hsiao, —Carry-select adder using single ripple carry adder, Electron. Lett., vol. 37, no. 10, pp. 614–615, May 2001.

- [6] J. M. Rabaey, Digtal Integrated Circuits—A Design Perspective. Upper Saddle River, NJ: Prentice-Hall, 2001.

- [7] Y. He, C. H. Chang, and J. Gu, —An area efficient 64-bit square root Carry-select adder for low power applications,

- [8] Cadence, —Encounter user guide, Version 6.2.4, March 2008.