# ISSN No: 2348-4845 International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

# **Implementation of High-Efficiency Adaptive Power Using VLSI**

#### **M.Sandhyavalli**

MTech Student Department of ECE Prasad Engineering College, Vikas Nagar,Siddipet Road Jangaon,Warangal District.

#### Sandeep Sunkari

Assistant Professor Department of ECE Prasad Engineering College, Vikas Nagar,Siddipet Road Jangaon,Warangal District.

#### Nihar

HoD Department of ECE Prasad Engineering College, Vikas Nagar,Siddipet Road Jangaon,Warangal District.

# ABSTRACT

High-efficiency input power range adaptive rectifier is presented. In this rectifier consists of two differential type sub-rectifiers and one control circuit unit . the proposed control unit circuit is used to detect the input power level by using sensing the converted output voltage rectifier is generating two control signals and to switch the rectifier between two operation modes. This IC chip device has been fabricated with 0.18- $\mu$ m CMOS technology. With two three-stage differential-type of rectifiers as the subrectifiers, the low power conversion efficiency (PCE) region is extended.

**Keyword :** Micro wind ,DSCH , adaptive, low power conversion efficiency (PCE) Region, rectifier.

#### **I INTRODUCTION**

The result of semiconductor technology, electronic circuits are becoming high complicated,

And the power consumption is increasing very high .However, the resulting in battery capacity is failed to receive the chip power consumption, this technique fallows Moore's law. To low power applications .like wireless sensor nodes and human interface devices, have been intensely researched and deployed. To extend the battery life for never ending or changing operation, a power and human consumption technique can be employed for use as an alternative power source. There are many types of power sources, such as ambient light ,vibration, thermal energy, radio frequency (RF) signal, and so on. This sources are different applications like wireless applications ,Wi-Fi and Bluetooth applications, to convert received RF signal into a DC voltage signals .and in this project rectifier is most important component .and different types of architectures are designed, and one of the most important application of rectifier is power consumption efficiency which is defined

#### PCE =Pout put/P input

In this principle P output is output is output power and P input is input power of the rectifier ,when the input power reaches certain level the power loss transistor will increase the faster than the output power, and many models and analyzes have been developed.

#### **II DESIGN TECHNIQUES**

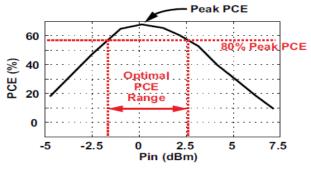

The harvesting and storing of the power in a power harvester requires a rectifier with high PCE. As shown in Fig. 1, a typical hill-shaped PCE curve as a function of two major input power functions, one is the peak PCE and other one optimal PCE range. The peak PCE is the maximum PCE and one rectifier can reach, At the peak PCE condition, the required input power level is defined by *P*in ,peak. At this input power level, the rectifier can operate most efficiently. Obviously, the PCE will drop when the input power is below this level since the rectifier pumps a lower voltage with a limited input power. Although the pumped-up voltage keeps going higher with a larger input power, the loss in the rectifier itself starts to increase faster than the power it can provide if the input power is larger than Pin, peak. This indicates the rectifier can only operate efficiently with in a certain input power range. The input power range over which the PCE of the rectifier is still more than 80% of its peak value is defined as the optimal PCE range of the rectifier. The optimal

**July 2015**

Volume No: 2 (2015), Issue No: 7 (July) www.iimetmr.com ISSN No: 2348-4845 International Journal & Magazine of Engineering, Technology, Management and Research A Peer Reviewed Open Access International Journal

PCE range describes the suitable input power range for a rectifier.

Fig 1. Typical PCE curve as a function of input power.

#### **III. PROPOSED ADAPTIVE RECTIFIE**

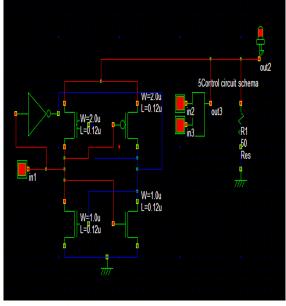

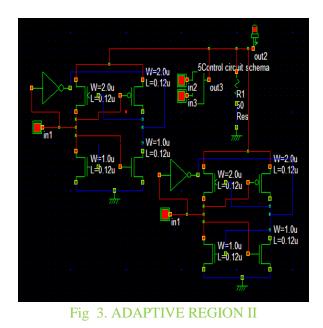

The proposed adaptive rectifier consists of two subrectifiers, a control circuit, and three transistor switches. The sub rectifiers scalable according to the RF input power and its harvested output voltage. In this brief, a three-stage differential-type rectifier is used. The sub-rectifiers receive differential RF input signals and then charge up the storing capacitors (included in the sub-rectifier block). The control circuit senses the output voltage of the rectifier Vout and generates two control signalsVctrl1 and Vctrl2 which will be used to control the transistor switches. R load is the loading resistor, and it is2-k\_ in this brief. The operation of the proposed adaptive rectifier can be divided into three regions as shown In Region I, the input power is very weak and therefore the output voltage is very small. Both control voltages are zero. The transistor Mp1 is turned on, and Mn1and Mn2 are turned off. The entire rectifier is operated by only one sub-rectifier, as shown in Fig. 5, and hence, the entire rectifier still works under this condition. Regions II and III correspond to the two major operation modes, i.e., parallel mode in Region II and series mode in Region III. when the input power is small (Region II), the control voltages Vctrl1 and Vctrl2 are equal to the high level (Vout) and ground, respectively. The transistors Mn1and Mp1 are turned on, and Mn2 is turned off. The whole circuit is now operating with the two sub-rectifiers in parallel, as shown in fig.

Fig 2ADAPTIVE REGION I

The input power is very weak and therefore the output voltage is very small. Both control voltages are zero. The transistor is turned on, and Mn1 and Mn2 are turned off. The entire rectifier is operated by only one sub-rectifier, and hence, the entire rectifier still works under this condition.

This circuit shows the parallel mode operation of the adaptive power region.

International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

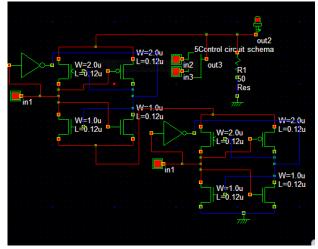

Fig 4 shows adaptive region III

This schematic shows the series mode operation of adaptive power region operation. The sub-rectifier is only needs to provide half of the loading current, and the rectifier can supply power is more efficient. Under this high input power level (Region III), on the other hand, the output voltage is Vout will be provided over the switching point and drive Vctrl1to a low voltage level and Vctrl2 to a high. The transistor *M*n2 is turned on, and the transistors *M*n1 and *M*p1 are turned off. The whole circuit is now equivalent to two sub-rectifiers in series that the circuit can increase the output voltage is Vout higher, providing more power to the load. The entire circuit can switch between these three regions according to the input power level adaptively by sensing the output voltage.

#### **Control unit operation**

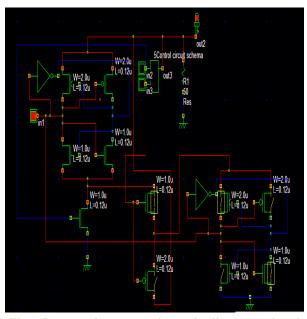

Fig 5 This circuit it shows the adaptive power operation in control unit technique

# IV DESIGN TECHNIQUES: Differential-Type Rectifier Circuit

This type of rectifiers are used for the sub-rectifiers in this operation . This unit cell is shown in The differential input signals are coupled to nodes A and B by the capacitors C1 and C2. The operation of the unit cell can be divided into two phases operations .In the phase that RF +in is positive and RF-in is negative, the transistor M2 is turned on and the current flows from the ground to node B. At the peak value , node B will be charged to the ground. Then, in the phase that RF+ in is negative and RF-in is positive ,node B will be pushed up and turn on the transistor M1. Node A is therefore charged up by the current flowing from the ground. At the peak, node B will be involved.

**ISSN No: 2348-4845**

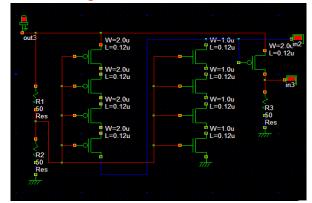

Fig 6 Proposed system schematic diagram related adaptive power

The proposed control circuit is shown where V out is the output voltage of the entire adaptive rectifier. To eliminate the maximum PCE, the control circuit has to reduce the minimum power. Hence, the resistors R1, R2, and R3 the ratio of V sg, p/V gs, n is equal to R1/R2, which is much larger than the unity. So the output voltage increases to zero. the proposed rectifier is activated even without the active control circuit

July 2015

# **V SIMULATION RESULT**

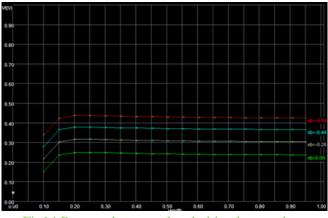

Proposed schematic diagram related simulation result

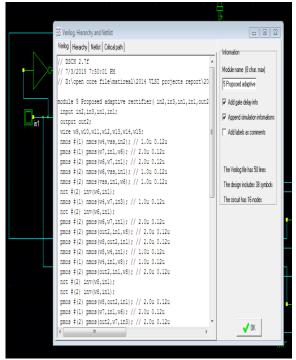

Fig 7 Verilog code generation related to proposed schematic diagram

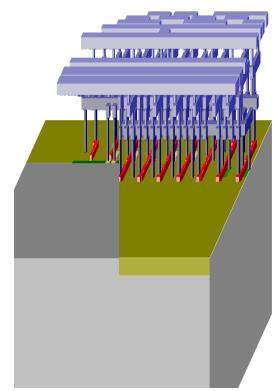

Fig 9.3D design for schematic diagram

Fig 8 layout diagram for proposed system

**July 2015**

**ISSN No: 2348-4845** International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

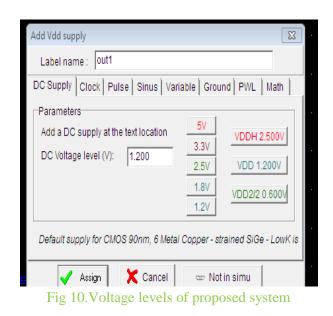

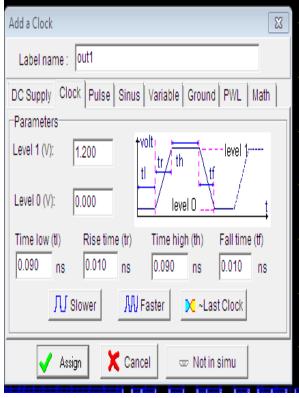

Fig 11.Clock signal generation

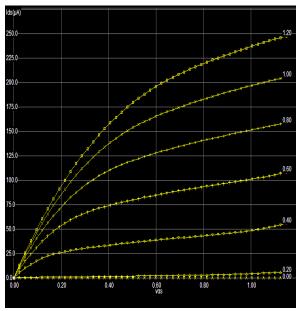

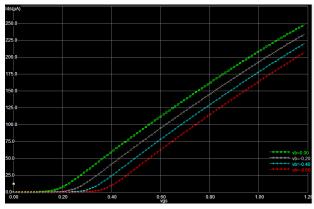

Fig 12.Characteristics of MOS transistor

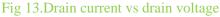

Fig14.Proposed system threshold voltage values

**July 2015**

International Journal & Magazine of Engineering, Technology, Management and Research

AND DESCRIPTION TO THE PROPERTY OF THE PROPERT

A Peer Reviewed Open Access International Journal

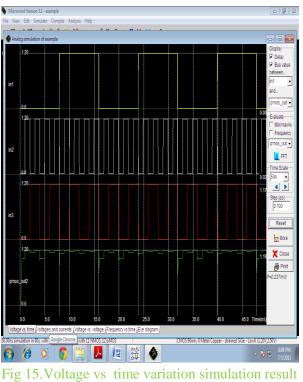

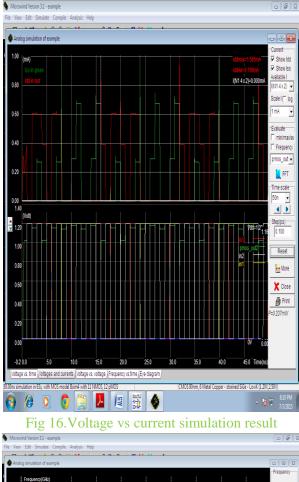

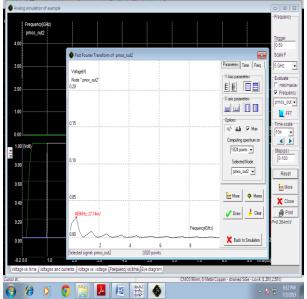

Fig 17.Frequency vs time related fft simulation result

### **VI CONCLUSTION**

The result of optimal low power adaptive PCE technique we find the maximum range of frequency is

100 MHZ, and the voltage is 158.9mv and the total current is 1.585mA the optimal power is calculated 0.251 wis required in our prose system we design new structure that has an extended optimal PCE range .Using a three-stage conventional differential-type rectifier as the sub rectifier,\an adaptive rectifier that can switch between parallel and series modes is proposed.

**ISSN No: 2348-4845**

#### **VII** References

1. N. J. Guilar, R. Amirtharajah, and P. J. Hurst, "A full-wave rectifierfor interfacing with multi-phase piezoelectric energy harvesters," in*Proc. Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2008,pp. 302–615.

2. K. Kotani, A. Sasaki, and T. Ito, "Highefficiency differential-driveCMOS rectifier for UHF RFIDs," *IEEE J. Solid-State Circuits*, vol. 44,no. 11, pp. 3011–3018, Nov. 2009.

3. J. Yi, W.-H. Ki, and C.-Y. Tsui, "Analysis and design strategy of UHFmicro-power CMOS rectifiers for micro-sensor and RFID applications,"*IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 1, pp. 153–166,Jan. 2007.

4. R. E. Barnett, J. Liu, and S. Lazar, "A RF to DC voltage conversion model for multi-stage rectifiers in UHF RFID transponders," *IEEE J.Solid-State Circuits*, vol. 44, no. 2, pp. 354–370, Feb. 2009.

5. A. Shameli, A. Safarian, A. Rofougaran, M. Rofougaran, and F. D.Flaviis, "Power harvester design for passive UHF RFID tag using a voltage boosting technique," *IEEE Trans. Microw. Theory Tech.*, vol. 55,no. 6, pp. 1089–1097, Jun. 2007.

Volume No: 2 (2015), Issue No: 7 (July) www.ijmetmr.com