A Peer Reviewed Open Access International Journal

# Low Power 8-Bit ALU Design Using Full Adder and Multiplexer Based on GDI Technique

#### **Mohd Shahid**

M.Tech Student

Al-Habeeb College of Engineering and Technology.

#### Abstract

Arithmetic logic unit (ALU) is an important part of microprocessor. In digital processor logical and arithmetic operation executes using ALU. In this paper we describes 8-bit ALU using low power 11-transistor full adder (FA) and Gate diffusion input (GDI) based multiplexer. By using FA and multiplexer, we have reduced power and delay of 8-bit ALU as compare to existing design. All design were simulated using Tanner EDA tool v15.0 in 32nm BSIM4 technology. Performance analyses were done with respect to power, delay and power delay product.

Keywords—8-bit ALU, Gate diffusion input (GDI), Full Adder.

#### INTRODUCTION

Exploitation of very large scale integration (VLSI) technology has developed to the point where millions of transistor can be implemented on a single chip. Complementary metal oxide semiconductor (CMOS) has been the backbone in mixed signal because it reducing power and providing good mix component for analog and digital design.

The mainstays of power consumption in CMOS circuits are static power  $(P_S)$ , dynamic power  $(P_d)$  and short circuit power  $(P_{SC})$ . Thus, the total power consumption  $(P_t)$  is

$$P_{t}=P_{s}+P_{d}+P_{sc} \qquad (1)$$

Ps is caused by leakage current between the diffusion region and the substrate. Pd consumes due to capacitive load and clock frequency and Pscis caused by short circuit current. Increasing number of transistors per chip area and scale down technologies have

Syed Samiuddin, M.Tech

Associate Professor,

Al-Habeeb College of Engineering and Technology.

consumed more power thus the main objective is to reduce the power consumption by using different techniques for improving performance of VLSI circuits.

ALU is the section of the computer processor that executes arithmetic and logical operation. ALU is an exclusively combinational logic circuit which means output changes with changing of input response. The ALU is a utile device in microprocessor, performing various logical and arithmetic operations [1].

#### **PREVIOUSWORK**

Power can be reduced either architecture level or module level or circuit level. In analog switch technique select input logic as a control logic and passes another input signal from gate terminal [4]. FA is a basic building block for designing ALU, different types of FA designing for minimizing powersuch as hybrid FA, low power 10 transistors FA and11transistor FA. FA operating in ultra-low mode by using sub threshold current and consumes low power [2]-[3]. FAbuild using low power XOR gates and 2 is to 1 multiplexer [7].

ALU design using FinFET technology has two gates which are electrically independent, minimize the complexity of the circuit and also reduce the power consumption due to reducing the leakage current. In FinFETtechnology "Fin" is a thin silicon which mould the body of the device [5]. ALU design using the reconfigurable logic of multi input floating gate metal oxide semiconductor (MIFG-MOS) transistor have multiple inputs, increased the functionality of the circuit. MIFG-MOS transistor gives ON and OFF states of the transistor by observing weighted sum of all inputs. MIFG-MOS transistor reducing the number of transistor

A Peer Reviewed Open Access International Journal

and complexity of the circuit, improve the performance of the circuit minimize the delay and reduced the power dissipation [6]. When channel length is scale down for designing circuits, metal gate and high-k dielectric is to be introduced. Metal gate and high-k dielectric gives extra channelength with output down the leakage current[8].

### **CIRCUIT DESIGN OFALU**

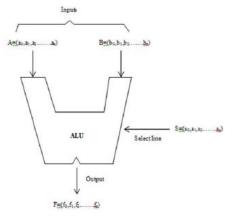

ALU is a core part of computer or digital processor that executes arithmetic and logical operation, such as increment, decrement, addition and subtraction as an arithmetic operation and AND, OR, XOR, XNOR as a logical operations as shown in table 1. The symbol of ALU is in fig1. ALU is build by using FA and multiplexer.

Fig. 1. Symbol of ALU

### TABLEI. TRUTHTABLEOFALU

| $S_2$ | $S_1$ | S <sub>0</sub> | OPERATION   |

|-------|-------|----------------|-------------|

| 0     | 0     | 0              | OR          |

| 0     | 0     | 1              | XNOR        |

| 0     | 1     | 0              | XOR         |

| 0     | 1     | 1              | AND         |

| 1     | 0     | 0              | INCREMENT   |

| 1     | 0     | 1              | ADDITION    |

| 1     | 1     | 0              | DECREMENT   |

| 1     | 1     | 1              | SUBTRACTION |

### 11 Transistor Full Adder (11TFA)

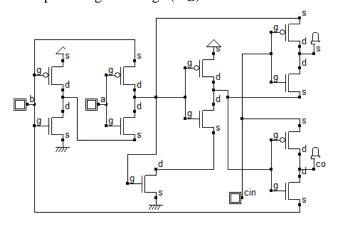

FA is basic functional module for designing ALU. 11T used for design of FA, this modern design of FA is minimize the power and reduced the delay. FA depicts in

Fig. 2, circuit is operating at power supply (VDD) 0.9V. Inputs A apply to the gate terminal of PMOS\_1 and NMOS\_1, drain terminal of PMOS\_2. Inputs B apply to the gate terminal of PMOS\_2 and PMOS\_2, drain terminal of NMOS\_1. When source voltage (VS) is greater than threshold voltage (VTH) transistor is ON and pass the signal from gate terminal to drain terminal means pass the gate voltage (VG) to drainterminal.

Fig. 2. Schematic of 11T FA

Thus, when input A is high, pass the input B vice versa. FA is build using low power XOR gates and 2 is to 1 multiplexer. XOR gates gives the sum output and multiplexer responsible for carry out (Cout). An extra transistor NMOS 6 operates in ultra-low mode using subthreshold current and consumes low power. At strong inversion region gate to source voltage (VGS) is higher than threshold voltage (VTH), majority carriers removed from the area of gate and minority carriers is produced, at weak inversion region VGS is below than VTH less minority carrier is produced, but their presence produce leakage current this current is called subthreshold current. This current can be used when VDD is below then VTH and run the circuit at ultra-low mode and consumes less power. 11T FA is operating at subthreshold mode by adding an extra transistor NMOS\_6.

### **GDI** basedMultiplexers

GDI technique is area efficient technique which consumes less power with reducing the number of transistor. GDI technique need twin well process or

A Peer Reviewed Open Access International Journal

silicon on insulator for chip composition. Twin well process gives separate optimization of n-type and p-type transistor and also optimizes gain and VTH of n-type and p-type device. Silicon on insulator combined both MOS and bipolar technologies into a single process.

GDI technique providing an extra input for the cell and maintain the circuit complexity. GDI technique solves the problem of poor ON to OFF transition characteristic of PMOS and providing the full swing at internal node of circuit. Fig. 3 depicts the 2 is to 1 multiplexer, select line S is common input for gate terminal of PMOS\_1 and NMOS\_1. Input A and Input B is connected to the source terminal of PMOS\_1 and NMOS\_1 respectively. When S is low then PMOS\_1 is ON and pass the input A from source terminal to drain terminal, when S is high NMOS\_1 is ON and PMOS\_1 is OFF. Output is common for drain terminal for PMOS\_1 and NMOS\_1.

Fig. 3. GDI based MUX 2

mux\_2

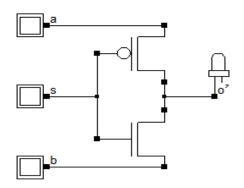

Fig. 4. GDI based MUX 4

Fig. 4 depicts the 4 is to 1 multiplexer, 4 is to 1 multiplexer design using three 2 is to 1 multiplexer.

Select lines S<sub>0</sub> and S<sub>1</sub> is worked as a switching input which is responsible for the high and low states of the transistor, S<sub>0</sub> is common input for gate terminal of PMOS\_1, PMOS\_2, NMOS\_1 and NMOS\_2, S<sub>1</sub> is common input for gate terminal of PMOS\_3 and NMOS\_3. Inputs are connected to the source terminal of transistor.

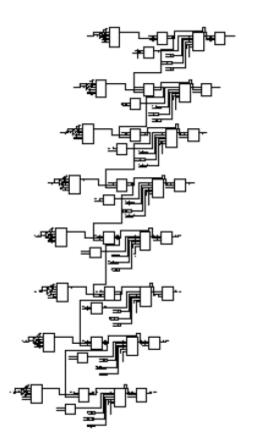

### **Design of 8-bitALU**

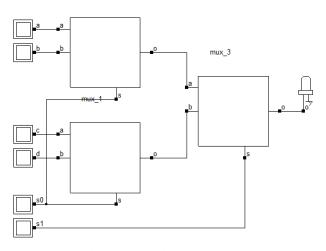

FA is mainstays of ALU, 8-bit ALU is design using 8-bit ripple carry adder (RCA). RCA is responsible for arithmetic operation of ALU. Other modules needed for designing ALU are 2 is to 1 multiplexer and 4 is to 1 multiplexer. Logical operation executes by using multiplexer. Fig.5 depicts the 1-bit ALU, 1-bit ALU design using two 4 is to 1 multiplexer and one 2 is to1 multiplexer and FA.

Fig. 5. 1-bit ALU

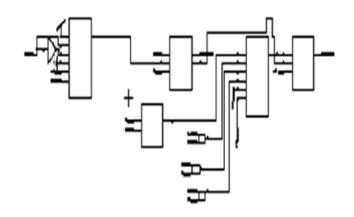

Fig. 6 depicts 8-bit ALU, RCA is basic building block of 8-bit ALU which is perform arithmetic operation. Input A (a0,a1,....a8) is apply in first input of RCA, Input B (b0,b1,...b8) is apply in first input of 4 is to 1 multiplexer and pass to the second input of RCA from output of 4 is to 1 multiplexer, and executes arithmetic operation. Logical operation executes through the cascading combination of 4 is to 1 multiplexer and 2 is to 1 multiplexer.

A Peer Reviewed Open Access International Journal

Fig. 6. 8-bit ALU

### SIMULATION ANDRESULT

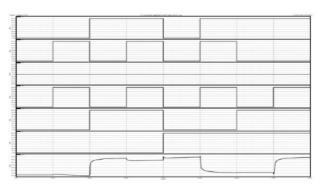

AlldesignistobesimulatedusingtanneredatoolW-editat transition time 80ns. Fig. 7 shows the waveform of 11T FA, at input combination "000" to "111". At "000", "010" and "110" problem is occur, this problem is solved by adding an extra transistorNMOS\_6.

Fig. 7. Waveform of 11-T FA

Fig. 8. Waveform of 1-bit ALU

Fig. 8 shows the waveform of 1-bit ALU. Simulation is done with select line combination "000" to "111". When select line S2 is high ALU performs logical operation and S2 is low ALU performs arithmetic operation. When select line combinationis "000" then ALU performs OR logical operation n and at "001", "010" and "011" combination ALU performs XNOR, XOR and AND logical operations respectively. From "100" to "111" combinations ALU performs arithmetic operation. At "010", "011" and "111" combination output gives 0.75V which is higher than the VTH, so we consider these outputs as alogic1.

Table II and Table III shows the comparison between CMOS logic based design and proposed design with respect to power, delay and power delay product at 32nm technology. Using proposed logic, 8-bit ALU consumes 31% less power as compare to CMOS logic based 8-bit ALU and also minimizes the delay.

# TABLEII. CMOS LOGIC BASED DESIGN AT 32NMTECHNOLOGY

| Design    | Power    | Delay   | PDP          |

|-----------|----------|---------|--------------|

| 14T FA    | 444.2nW  | 40.15ns | 17834nW*ns   |

| MUX2      | 270nW    | 40.68ns | 10983nW*ns   |

| MUX4      | 795nW    | 21ns    | 16695nW*ns   |

| 1-bit ALU | 4.91μW   | 32.47ns | 159.42 μW*ns |

| 8-bit ALU | 47.64 μW | 31.8ns  | 1514.9 μW*ns |

A Peer Reviewed Open Access International Journal

# TABLE III. PROPOSED LOGIC BASED DESIGN AT 32NM TECHNOLOGY

| Design            | Power   | Delay   | PDP          |

|-------------------|---------|---------|--------------|

| 11T FA            | 33nW    | 89.62ps | 2957nW*ps    |

| GDI based<br>MUX2 | 68.8nW  | 15.83ps | 1089nW*ps    |

| GDI based<br>MUX4 | 289nW   | 20ns    | 5780nW*ns    |

| 1-bit ALU         | 4.47μW  | 20.33ns | 90.87 μW*ns  |

| 8-bit ALU         | 32.9 μW | 6.95ns  | 228.65 μW*ns |

#### **CONCLUSION**

In this paper, 8-bit ALU design using 11-T FA and GDI based multiplexer at 32nm technology. At 32nm technology high-k dielectric and metal gate is to be introduced. There are three main sources responsible for occurring leakage current are the gate direct tunneling current, the subthreshold leakage current and reverse biased junction leakage. High-k dielectric is permitted to increase the gate capacitance and reduced the leakage power due to gate direct tunneling current. Metal gate make better strain capacity. Subthreshold leakage current is to be used at subthreshold mode and consumes low power. Finally, 8-bit ALU performs better as compare to existing design and consumes low power.

#### **REFERENCES**

- [1] T. Esther Rani, M.A. Rani and R. Rao, "AREA optimized low power arithmetic and logic unit," IEEE International Conference on Electronics Computer Technology, April 2011, pp.224–228.

- [2] Gangadhar Reddy Ramireddy "A Novel Power-Aware and High Performance Full Adder Cell for Ultra low Power Design," IEEE International Conference on Circuit, Power and Computing Technologies, 2014, pp.1121-1126.

- [3] JVR Ravindra, Gangadhar Reddy Ramireddy and HarikrishnaKamatham, "Design of Ultra Low Power

Full Adder using Modified Branch Based Logic Style," IEEE European Modelling Symposium, 2013, pp.691-696.

- [4] Rajesh Parihar, NidhiTiwari, AdityaMandloi and Dr.Binod Kumar, "An Implementation of 1-Bit Low Power Full Adder Based on Multiplexer and Pass Transistor Logic," IEEE International Conference on Information Communication and Embedded System, 2014, pp. 101-103.

- [5] L. Dhulipalla and A. Deepak, "Design and implementation Of 4-bit ALU using FINFETS for nanoscaletechnology," IEEE International Conference on Nanoscience, Engineering and Technology, November 2011, pp.190–195.

- [6] A. Srivastava and C. Srinivasan, "ALU Design Using Reconfigurable CMOS Logic," IEEE 45<sup>th</sup>midwest symposium on circuit and system, vol. 2, August 2002, pp. 663-666.

- [7] Ravi Tiwari and KhemrajDeshmukh, "Design and analysis of lowpower 11-transistor full adder," IJAREEIE, vol. 3, issue 6, June 2014,pp. 10301-10307.

- [8] PoojaVaishnav and Mr.VishalMoyal, "Performance Analysis Of 8-BitALU For Power In 32 Nm Scale," IJERT, vol. 1, issue 8, October 2012pp. 1-3.

Volume No: 4 (2017), Issue No: 7 (July) www.ijmetmr.com