A Peer Reviewed Open Access International Journal

# A Wide Range PLL Using Self-Healing Prescaler/VCO in CMOS

M.Srilakshmi

PG scholar VLSI Design,

Sir C R Reddy College of Engineering.

K. Archana

Assistant Professor,

Sir C R Reddy College of Engineering.

#### **Abstract:**

A phase locked loop is widely employed in wireline and wireless communication systems. The design of frequency synthesizer, often implemented by a phase locked loop (PLL), is a challenging task for RF designers in terms of power dissipation. The variability and leakage current in nanoscale CMOS technology may degrade the circuit performances. To accommodate those issues in a wide range phase locked loop (PLL), a self-healing prescaler and a self-healing voltage controlled oscillator (VCO) are used. A CMOS fully programmable 1 MHz resolution divider for Zigbee and IEEE 802.15.4 applications is implemented based on pulseswallow topology which uses the proposed ultra-low power divide by 32/33/47/48 multimodulus prescaler. A self-healing divide by 2/3 prescaler is the basic building block for designing of multimodulus prescaler. This proposed fully programmable multimodulus prescaler can consume an average power of 18.09µW.

#### **Index Terms:**

Phase locked loop, Frequency synthesizer, Self-Healing prescaler, VCO, Leakage current, Multimodulus prescaler.

#### **I.INTRODUCTION:**

Complementary-metal-oxide-semiconductor (CMOS) [1] is a technology for constructing integrated circuits. CMOS technology is used for analog [1] highly integrated transceivers for many types of communications. Two important characteristics of CMOS devices are high noise immunity and low static power consumption.

A phase locked loop [4] is a control system that generates an output signal whose phase is related to the phase of an input signal. PLL is a feedback system that combines a voltage controlled oscillator (VCO) [4] and a phase comparator so connected that the oscillator maintains a constant phase angle relative to a reference signal. PLLs are used to generate a stable output high frequency signals from a fixed low frequency signal. When a CMOS technology approaches to a nanometer scale the non-idealities such as variability and leakage current, may significantly affect the circuit performances. The process variability leads to the large variations to degrade the device matching and performances. It may result in a few dies on a wafer to meet the target performance specifications.

The undesired leakage currents also degrade the accuracy and resolution of the circuits. A phase locked loop (PLL) is widely employed in wire-line and wireless communication systems. The poor device matching and leakage current [5], [7] vary the common-mode voltage of a ring based voltage-controlled oscillator (VCO) over wide frequency range. It may limit the oscillation frequency range of a VCO [6] and causes a VCO not o oscillate in a worst case. To realize a wide range PLL, the divider following a VCO should be operate between the highest and lowest frequencies.

There are many applications that require the synthesis of frequencies above 3GHz. However, this range is generally beyond the maximum frequency range that PLL devices can directly accept. By using an external prescaler [3], the range of PLL can be extended. When a PLL works at a higher frequency which the static circuits cannot operate, dynamic circuits are needed.

A Peer Reviewed Open Access International Journal

#### **II.EXISTING CIRCUIT DESCRIPTION**

## A.Self-Healing Divide-by-4/5 Dual-Modulus Prescaler

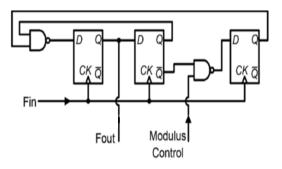

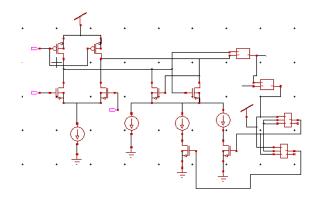

Fig. 2(a) shows a conventional divide-by-4/5 dual-modulus prescaler using TSPC DFFs [3]. The undesired leakage current [2] may charge or discharge to alter the states of the nodes A, B, AND Qbar in this TSPCDFF.

Fig.1. Conventional self-healing divide by 4/5 dual modulus prescaler.

The DFF is designed by using a method True Single Phase Clocking (TSPC) approach. TSPC is a dynamic CMOS approach to designing low power circuits. A TSPC prescaler must work over a wide frequency range to cover the process and temperature variations. For a TSPC prescaler, the undesired leakage currents may limit its frequency range or alter the original states of the floating nodes to have a malfunction.

Fig. 1(a) internal circuit of TSPC DFF.

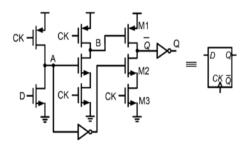

To detect and heal the above issues occurred at the nodes A and Qbar, the self-healing circuit is used. This self-healing circuit consists of a detector and three compensators. By using a self-healing circuit, the timing diagrams of a TPSC DFF with and without a malfunction are shown below.

Fig. 1(b) self-healing circuit for prescaler.

#### **B.Self-Healing VCO:**

A self-healing VCO is realized by four gain stages, a bottom-level detector, and a current compensator. Fig. 2 shows a bottom-level detector, a current compensator, and a gain stage. The cross-coupled pail, M5 and M6, enhances the output swing of this VCO. The output common-mode voltage and the output swing of the VCO are altered by the leakage currents, the total tail currents and the resistance of M3 and M4The bottom-level detector is shown in Fig. 2 and it detects the bottom-level of the VCO's output swing. A self-biased buffer enlarges the output of a VCO into a rail-to-rail swing. So, the output, Vbuf, of this self-biased buffer and Vout+ have the same polarity. When Vout+ goes high and Vbuf is high, the NOR gate will enable MB1 and disable MB2, respectively. The current of the transistor MB1 will charge the capacitor, CH, to increase VBL. The capacitor CH is used to track the bottom level of the VCO swing. The current compensators enables he tail currents when the bottom level is higher than the target swing voltage.

Fig. 2 gain stage of Voltage Controlled Oscillator.

A Peer Reviewed Open Access International Journal

For the current compensator a reference voltage Vsw represents the target bottom level of the VCO's swing and it is compared with Vbl, by a comparator. When the VCO's bottom level is smaller than the target one or the output common mode voltage of this VCO is high enough, Vbl is larger than Vsw. Then, the output of the comparator goes high and enables Q1. The current compensator enables the auxiliary tail current I1 to lower the output common-mode voltage. Then, it reduces the VCO's bottom level to be lower than Vsw. If the above case is not true, Q2 will be enabled and turn on the auxiliary tail current I2. It further lowers the VCO's bottom level.

#### **C.Phase locked loop:**

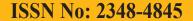

The PLL [8] is composed of a phase-frequency detector (PFD), a digital-controlled CP, a lock detector (LD), a time-to-digital converter (TDC) [8] with a 4-bit encoder, a self-healing VCO, a programmable divider, and a second-order passive loop filter. The programmable divider is composed of a 5-bit counter, a 3-bit swallow counter, a modulus control, and a self-healing divide-by-4/5 prescaler. The division ratio is from 4 to 131.

Fig. 3 The existing PLL.

#### **D.Counter:**

The programmable counter consists of a self-healing divide by 4/5 prescaler with fractional counter those are 5-bit counter and 3-bit swallow counter.

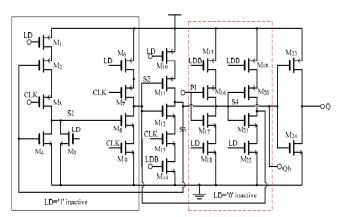

Fig. 4 Basic building block of programmable counter.

The basic cell is a CMOS circuit having LD, LDbar, CLK and PI signals as shown in fig. 4. These counters are used to get the division ratios from 4 to 131. The 5-bit p-counter consists of 5 basic cells and swallow counter having three basic cells.

#### Table 1 Operation of the basic cell:

| Load(LD) | Programmable input(PI) | Output(Q) |

|----------|------------------------|-----------|

| 0        | 0                      | CLK/2     |

| 0        | 1                      | CLK/2     |

| 1        | 0                      | 0         |

| 1        | 1                      | 1         |

When LD signal is low then the cell operates in divide by 2 mode otherwise output follows the programmable input. Once the programmable input (PI) of the each reloadable FF is loaded with a value and LD signal goes low, the P-counter begins to count down. Under this condition, the right hand side of the reloadable DFF as highlighted in Fig.4.4 is deactivated and transistor M5 is turned-off such that the FF acts as a divide-by-2 circuit where node S<sub>3</sub> is complimentary of the divideby-2 output. The FF remains in the divide-by-2 mode until the counter reaches the state "0000010". When LD='1', the first two stages of the reloadable FF is deactivated and node S1 always remains at logic 'o' since the transistor M5 is turned-on. Since node S1 is at logic 'o', node S2 should be at logic '1'. However, node S2 is overridden by the complimentary value of node S4. Under this condition (LD='1'), if the programmable input PI='0', nodes S4 and S2 switch to logic '1' and '0' respectively. The value at node S2 is latched to the output node Q on the next rising edge of the clock. Similarly, if PI='1', the output Q switches to '1' on the clock rising edge. However when LD='o', the bit-cell acts as a divide-by-2 circuit irrespective of the PI value.

A Peer Reviewed Open Access International Journal

The VCO operating range of the existing PLL is 60 to 1489MHz.s and the ref. frequency of this VCO is 15MHz. We can increase the operating frequencies of this VCO and then we get high frequencies by using prescaler. In order to get very wide ranges or the frequencies used for IEEE applications we go for multimodulus prescalers. The proposed multimodulus prescaler having division ratios of divide by 32/33/47/48. In this I used divide by 2/3 dual-modulus prescaler as a basic block.

#### **III.PROPOSED MULTIMODULUS PRESCALER:**

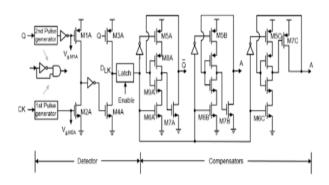

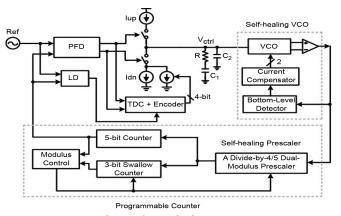

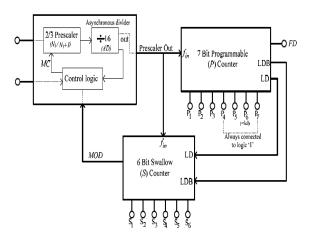

The proposed multimodulus prescaler [11] contains a divide by 2/3 dual modulus prescaler [11] followed by a MOD-16 counter and 7-bit programmable counter and a 5-bit swallow counter as shown in Fig. 5. This proposed multimodulus prescaler is designed in CMOS [1] 45nm technology to reduce the occupation of area and power consumption.

Fig. 5 Fully programmable multimodulus prescaler.

A CMOS fully programmable 1 MHz resolution divider for Zigbee and IEEE 802.15.4 applications is implemented based on pulse-swallow topology which uses the proposed ultra-low power 2/3 prescaler, low power 32/33/47/48 prescaler and a reloadable D flip-flop for the counters. A detailed design of wide-band 2/3 prescaler [11],[10],[9] based on dynamic logic is presented which is suitable for IEEE 802.11 a/b/g applications and also verified in the design of fully Programmable multimodulus prescaler as shown in Fig. 6.

Fig. 6. Divide by 32/33/47/48 multimodulus prescaler.

#### **A.MULTIMODULUS PRESCALER OPERATION:**

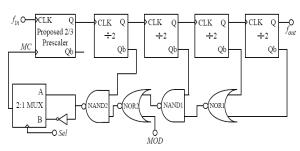

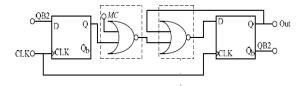

Fig. 6(a) Divide by 2/3 dual modulus prescaler

The divide by 2/3 dual modulus prescaler consists of two DFFs and two NOR gates. Fig. 6(a) shows the divide by 2/3 dual modulus prescaler using TSPC DFFs. The DFF is a TSPC DFF to reduce the power consumption and is works at high frequencies. If mode control signal is 0 then the dual modulus prescaler works as divide by 3 prescaler. If the mode control is 1 then the dual modulus prescaler acts as divide by 2 prescaler.

A fully programmable multimodulus prescaler operation is depends on sel signal. If sel is 0 and mod is 1 then the multimodulus prescaler acts as divide by 32 and mod is 0 then it acts as divide by 33 prescaler. If sel is 1 and mod is 0 then it acts as divide by 47 and mod is 1 then it acts as divide by 48 prescaler. The design can be progressed in CMOS 45nm technology.

#### **IV.EXPERIMENTAL RESULTS:**

When this PLL locks, the LD (Lock Detector) is enabled to turn on the TDC and an encoder. A 4-bit TDC digitizes this static phase error to reflect the amount of the current mismatching. Then, the digital code of this TDC is used to calibrate the charge pump. The CP calibration can be finished quickly due to this digital calibration. Once the calibration is completed, the digital code is fixed and the TDC is power-downed to save a power.

A Peer Reviewed Open Access International Journal

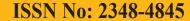

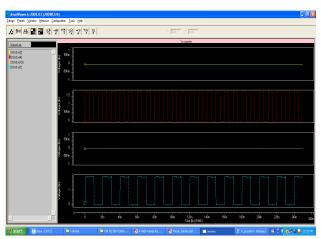

Fig. 7 simulation results of divide by 4/5 dual modulus prescaler.

The simulation results of the self-healing TSPC divide by 4/5 dual modulus prescaler is shown in Fig. 7. Which consume a power of 50µW when we simulate this in CMOS 65nm technology. The fully programmable counter can consume an average power of 0.11mW when we simulate this in CMOS 65nm technology.

Fig. 8 The simulation result of fully programmable 4/5 divider.

The simulation result of programmable counter is shown in Fig. 8.

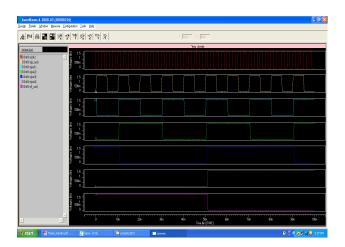

Fig. 9. The simulation result of VCO gain stage.

The VCO gain stage converts the analog signal to digital. Which is act as a CLK to the prescaler.

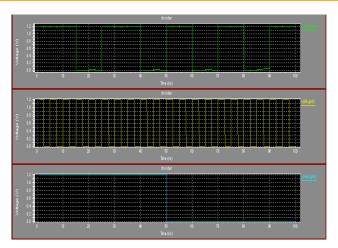

Fig. 10 Simulation result of counter basic cell when LD=0 and Pl=0.

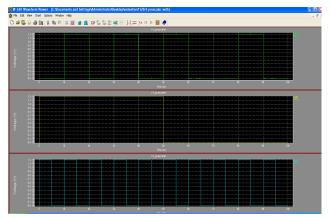

The non-idealities such as leakage current [2] and process variations can alter the VCO [6] gain in order to rectify those problems current compensators are used. As shown in Fig. 10 we know that when the LD=0 and PI is either 0 or 1 the output of the counter will be CLk divided by 2. Divided by 2 operation takes place here. These types of operations takes place in both programmable and swallow counters. In the proposed PLL [9] we have fully programmable multimodulus prescaler as shown in Fig. 5. In this we have a basic building block as TSPC divide by 2/3 dual modulus prescaler [10] as shown in Fig. 6. The simulation result of this divide by 2/3 prescaler is shown in Fig. 11. The average power consumed for this divide by 2/3 dual modulus prescaler [10] is 3.6µW when we simulate this in CMOS 45nm technology.

A Peer Reviewed Open Access International Journal

Fig. 11 Simulation result of divide by 2/3 TSPC dual modulus prescaler.

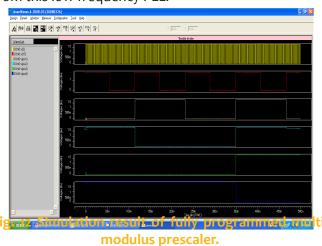

Fig. 12 shows the simulation result of the proposed fully programmable multimodulus prescaler. This multimodulus prescaler is used to extend the frequencies up to 6 GHz. Here the proposed multimodulus prescaler [11] is a CMOS fully programmable 1 MHz resolution divider for Zigbee and IEEE 802.15.4 applications is implemented based on pulse swallow topology. The range of P values among 74 to 77 then the P-counter can produce 2.4 GHz frequency which is used for Zigbee application. In this the multimodulus prescaler acts as divide by 32/33 dual modulus prescaler [11]. For IEEE 802.15.4 application the multimodulus prescaler can be operating in divide by 47/48 dual modulus prescaler [9], [10]. Here also the programmable counter will have 1MHz resolution signal can be applied to P-counter. P values ranging from 105 to 122. It can generate frequency ranges from 5.1 GHz to 5.82 GHz. The fully programmed multimodulus prescaler [9] can consume an average power of 18.09µW when we simulate this in CMOS 45nm technology. The simulation result is shown in Fig 12. We can extend the divide ratios by altering the P-values and S-values. Thus we can achieve more high frequencies from this low frequency PLL.

#### **V.CONCLUSION:**

A wide-range PLL is designed in a 45-nm CMOS process. To deal with the process variability and leakage current in nanoscale CMOS process, a self-healing fully programmable multimodulus prescaler and a self-healing VCO are presented. The multimodulus prescaler can be able to operate accurately in a wide band from 1 MHz to 6 GHz. The core circuit occupies extremely tiny area and it consumes a less amount of power. Experimental results are given to demonstrate the feasibility.

#### **VI.ACKNOWLEDGMENT:**

I am greatly indebted to my advisor Miss K. Archana for her valuable guidance, consistent encouragement and emphasis on the quality of the research contribution. Finally, and most importantly i would like to thank my family and friends for their support and unconditional love i have enjoyed throughout my life.

#### **VII.REFERENCES:**

- [1] L. L. Lewyn, T. Ytterdal, C. Wulff, and K. Martin, "Analog circuit design in nanoscale CMOS technologies," Proc. IEEE, vol. 18, no. 11, pp. 1687–1714, Oct. 2009.

- [2] R. Holzer, "A 1 V CMOS PLL designed in high-leakage CMOS process operating at 10–700 MHz," in Proc. IEEE Int. Solid-State Circuits Conf., 2002, pp. 272–273.

- [3] C. Y. Yang, G. K. Dehng, J. M. Hsu, and S. I. Liu, "New dynamic flip-flops for high-speed dual modulus prescaler," IEEE J. Solid-State Circuits, vol. 33, no. 10, pp. 1568–1571, Oct. 1998.

- [4] C. N. Chuang and S. I. Liu, "A 1 V phase locked loop with leakage compensation in 0.13 m CMOS technology," IEICE Trans. Electron., vol. E89-C, pp. 295–299, Mar. 2006.

- [5] C. C. Hung and S. I. Liu, "A leakage-suppression technique for phase locked systems in 65 nm CMOS technology," in Proc. IEEE Int. Solid- State Circuits Conf., 2009, pp. 400–401.

- [6] N. Fong, J. Plouchart, N. Zamdmer, D. Liu, L. Wagner, C.Plett, and N. Tarr, "Design of wide-band CMOS VCO for multiband wireless LAN applications", IEEE J. Solid-State Circuits (JSSC), vol. 38, no.8, pp. 1333-1342, Aug. 2003.

ISSN No: 2348-4845

### International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

[7] P. Andreani, "A low phase noise, low phase error 1.8-GHz quadrature CMOS VCO", Proc. Of 2002 IEEE ISSCC, pp. 290-291, Feb. 2006.

[8] Won-Hyo Lee, Jun-Dong Cho and Sung-Dae Lee, "A high speed and low power phase frequency detector and charge pump", in Proc. IEEE Biomedical Circuits & Systems Conf., pp. 187-190, Nov 2007.

[9] Xinhua He, "Low Phase Noise CMOS PLL Frequency synthesizer Analysis and Design", Ph.D. Thesis, Graduate Studies of the University of Maryland, 2007.

[10] V. Manassewitsch, Frequency Synthesizers, Theory and Design, Wiley, 1987. Ultra Low Power CMOS Phase-Locked Loop Synthesizers.

[11] M.Vamshi Krishna, M.A. Do, K.S. Yeo, C.C. Boon and W.M. Lim, "Design and Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler", IEEE Trans. Circuits & Systems-I: Reg. Papers, vol. 57, no.1, pp. 72-82, Jan. 2010.

#### **About Author's:**

#### Miss.M.Srilakshmi

received B.Tech degree in Electronics and communication from Paladugu Nagaiah Chowdary & Vijay Institute of Engineering and Technology, Acharya Nagarjuna university, Kakinada, in 2012. Currently pursuing M.Tech in VLSI Design from Sir C R Reddy College of Engineering, Eluru, India. Her area of interest is low power VLSI Design.

#### Miss.K.Archana

received the B.Tech degree in Electronics and communication from Nizam institute of engineering and technology, Jawaharlal Nehru technological university, India, in 2006, and the M.Tech degree in VLSI & Embedded Systems from Jawaharlal Nehru technological University, Kakinada, in 2012. Her research interests include low-power computing, real-time embedded systems, and operating systems.