## ISSN No: 2348-4845 International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

# **Design and Implementation of a Reversible Central Processing Unit**

# <sup>1</sup>M.Tech, Joginpally BR Engineering College. <sup>2</sup>M.S, MTech, (Ph.D), (ECE), P.G. Diploma, Y.L.S.I.(ISO UKAS Certified), Professor and Dean-R&D Cell & ECE, Realtime I.T.E.D.A Software Industry Cell.

#### Abstract:

One-to-one mapping from input to output is the necessary condition for a reversible computational model transiting from one state of abstract machine to another. Probably, the biggest motivation to study reversible technologies is that, it is considered to be the best effective way to enhance the energy efficiency than the conventional models. The research on reversibility has shown greater impact to have enormous applications in emerging technologies such as Quantum Computing, QCA, Nanotechnology and Low Power VLSI.

In this paper, we have realized novel reversible architecture components of Central Processing Unit (CPU). The Central Processing Unit (CPU) is the primary component of a computer that processes instructions. It runs the operating system and applications, constantly receiving input from the user or active software programs. It processes the data and produces output, which may store by an application or displayed on the screen. The proposed design is synthesized and simulated on xilinx14.4 ISE and the simulation result verifies the correctness of the proposed design.

#### **Index Terms:**

Reversible Logic, Reversible ALU, Reversible Flip Flops and registers, Reversible CPU, Quantum Cost, Garbage Output.

#### **I.INTRODUCTION:**

Power crisis is a vital problem in today's world. In recent years, the growing market of electronic systems suffers from power dissipation and heat removal problem. If more and more power is dissipated, system becomes overheated which reduces the life time of the electronic system. The need of microelectronic circuits dissipation with low power leads to the implementation of reversible logic circuit. Bennett [1] proved that the one-to-one mapping between the inputs and outputs of reversible circuit drastically reduces the power consumption and heat dissipation of a circuit. security digital computing Today in and communications is of prime importance and therefore cryptographic protocols play a major role. David [2] proved that reversibility plays a vital role in quantum computation. Quantum gates and reversible logic gates are closely related to each other. Like classical reversible circuits, the number of input quantum bits must be equal to the number of output quantum bits. The quantum gates and circuits must be reversible.

So, the quantum circuits can directly be designed from reversible circuits. Processor design is indeed a difficult task and thinking the organization and architecture of the design in reversible way requires a lot of works. The irreversible processors dissipate a significant amount of heat and they require more power than the corresponding reversible one. A reversible processor can overcome these problems. As reversible computing is a new era, very few works [3], [4] regarding reversible processor have been done.

A Peer Reviewed Open Access International Journal

As well as, there is no established patent work in this area. The existing reversible processor architectures [3], [4] lack rigor and completeness. These parameters motivate this work of reversible processor design. In this work, we present a logical reversible processor design architecture and algorithms that try to fill up the gap between realization of the reversible architecture and completeness of the design.

## **II. BACKGROUND WORK:**

One of the major goals in modern circuit design is reduction of power consumption. As demonstrated by R.Landauer in the early 1960s, irreversible hardware computation, regardless of its realization technique, results in energy dissipation due to the information loss [1]. Reversible logic circuits have theoretically zero internal power dissipation because they do not lose information. Hence,. In 1973, Bennett showed that in order to avoid KTln2 joules of energy dissipation in a circuit, it must be built using reversible logic gates [2]. A circuit is said to be reversible if the input vector can be uniquely recovered from the output vector and there is a one-to-one correspondence between its input and output assignments, i.e. not only the output

## A. Reversible Gate:

Reversible gate is an n-input and n-output (denoted by  $n \times n$ ) circuit that produces a unique output pattern for each possible input pattern. In other words, reversible gates are circuits in which the number of outputs is equal to the number of inputs and there is a one-to-one correspondence between the vector of inputs and outputs.

## **B.** Garbage Output:

Unwanted or unused output of a reversible gate (or circuit) is known as garbage output, i.e., the output(s) which is(are) needed only to maintain the reversibility is (are) known as garbage output(s).

## C. Quantum Cost:

The quantum cost can be derived by substituting the reversible gates of a circuit by a cascade of elementary

quantum gates [5]. Elementary quantum gates realize quantum circuits that are inherently reversible and manipulate qubits rather than pure logic values. The state of a qubit for two pure logic states can be expressed as  $|\psi\rangle = \alpha |0\rangle + \beta |1\rangle$ , where  $|0\rangle$  and  $|1\rangle$ > denote 0 and 1, respectively, and and $\alpha$  and  $\beta$  are complex numbers such that  $|\alpha| 2 + |\beta| 2 = 1$ . The most used elementary quantum gates are the NOT gate, the controlled-NOT (CNOT) gate, the controlled-V gate and the controlled-V+ gate

## **III. PROPOSED WORK:**

The internal arrangement of a microprocessor varies depending on the design and the intended purposes of the microprocessor. A microprocessor includes an arithmetic logic unit (ALU) and a control unit (CU) section. These two sections are connected to memory and I/O by buses which carry information and signal between the units. They have a defined datapath. The ALU performs the arithmetic and logical operations. The control logic section retrieves instruction operation codes from memory, and initiates whatever sequence of operations of the ALU requires to carry out the instruction. A single operation code affects many individual datapaths, registers, and other elements of the processor. Following steps are considered to design the desired reversible central processing unit (CPU):

- Design the overall structure elements of the reversible CPU.

- Design the reversible realizations of the flip-flops.

- Design the reversible memory circuits (such as buffer registers and counter circuits) using the proposed reversible flip-flops of the previous step.

- Design the arithmetic circuits such as adder, multiplier, divider, comparator etc.

- Design the reversible realization of ALU.

- Design the reversible control unit of the processor by designing an efficient instruction decoder.

- Construct the necessary logic to control the datapath.

- Realize the overall architecture and organization of the proposed reversible processor.

• Analysis of the proposed reversible central processing unit in terms of cost and performance efficiency.

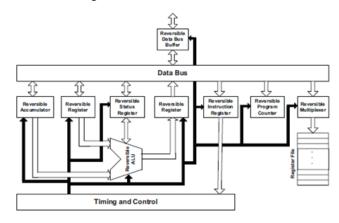

The architecture of the proposed reversible processor is shown in Fig.

## Fig: Outline of the Design of the Proposed Reversible Processor

The data path of the proposed reversible processor is shown in Fig: The control signals are not shown in the diagram for simplicity.According to the block diagram and the data path design the proposed reversible processor has been divided into small components. The reversible realizations of the proposed components are discussed in the following subsections.

Fig: Data path Design of the Proposed Reversible Processor

A. Proposed Reversible Memory Components:

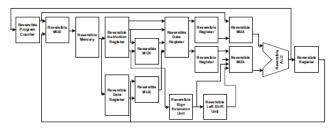

Flip-flops (FF) are the basic elements of a register. We use template matching algorithm to propose a reversible J-K FF with minimum quantum cost. This J-K FF is used to design the instruction register. We propose a new reversible gate, namely BJ gate , to design a reversible J-K FF. The proposed reversible J-K FF requires only one gate, it produces only one

Volume No: 3 (2016), Issue No: 6 (June) www.ijmetmr.com garbage output and it has 12 quantum cost. The design of the proposed J-K FF is shown in Fig. The proposed reversible J-K FF achieves the improvement of 66.6% in terms of number of gates, 66.6% in terms of garbage outputs, 66.6% in terms of delay and 4.28% in terms of quantum cost over the existing best one[9].

#### Fig. 3. Proposed Reversible J-K Flip-Flop

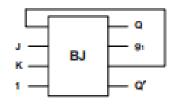

This proposed J-K FF is used to design the registers. A reversible 16-bit register can be designed using sixteen HNFG gates and sixteen proposed J-K FFs. The J-K FFs take the inputs through HNFG gates and with the change of the clock pulse they produce the normal and complemented outputs.

instruction register.

**June 2016**

A Peer Reviewed Open Access International Journal

The sequence counter is also designed using four proposed J-K FFs and four Feynman gates.

The J-K FFs change states with the positive clock edge and the counter counts from 0 to 15. This optimized design of sequence counter produces 4 garbage outputs.

# Fig. 5.Proposed design of 4-bit reversible sequence counter.

#### **B.** Proposed Reversible Multiplexer Reversible:

Multiplexer (Mux) is required to select a certain input from various input sources. A reversible 4-to-1 mux is designed with Fredkin gates. The proposed design of 4-to-1 mux is shown in Fig. 6. The proposed reversible 4-to-1 mux achieves the improvement of 57.14% in terms of number of gates, 54.54% in terms of garbage outputs, 73.68% in terms of quantum cost and 57.14% in terms of delay over the existing best one [10].

## Fig. 6. Proposed Reversible 4-to-1 Multiplexer C. Proposed Reversible Decoder:

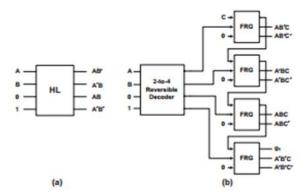

The control unit requires decoders to decode the instructions. We propose the design of an n-to-2<sup>n</sup> decoder. To design this decoder at first we propose a reversible 2-to-4 decoder which was used to construct a 3-to-8 decoder and so on. The design of an improved 2-to-4 decoder was very challenging as an existing 2-to-4 decoder [11] requires only one gate and it does not produce any garbage outputs. So, there was no scope to improve gate count, garbage outputs and delay. Exhaustive search was used to find the reversible gate with optimal solution which produces the minimum quantum cost.

Volume No: 3 (2016), Issue No: 6 (June) www.ijmetmr.com We propose a new reversible gate, namely HL gate [8] to design a 2-to-4 decoder. The proposed 2-to-4 decoder requires only one gate without any garbage output which has 7 quantum cost. Our proposed design has the same gate count, garbage outputs and delay. But it has improved quantum cost. A reversible 3-to-8 decoder can be designed using one 2-to-4 reversible decoder and four Fredkin gates. The achievement of the design of 3-to-8 design was greater as the existing best 3-to-8 decoder [12] is not much optimized. The designs of the proposed reversible 2-to-4 decoder and 3-to-8 decoder are shown in Fig. 7(a) and Fig. 7(b) respectively.

Fig. 7. Proposed Reversible (a) 2-to-4 Decoder (b) 3-to-8 Decoder

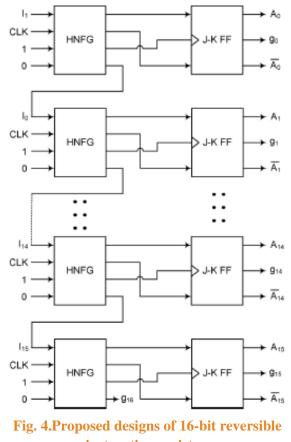

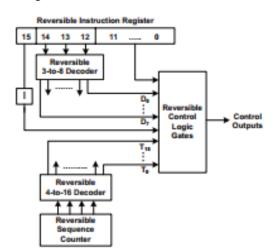

#### **D.** Proposed Reversible Control Unit:

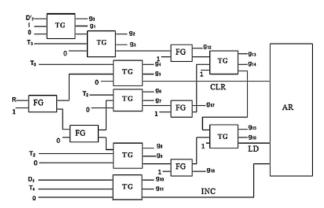

A control unit is a circuit that directs operations within the computer's processor by directing the input and output of a computer system. The control unit consists of two decoders, a sequence counter, and a number of control logic gates. It fetches the instruction from instruction register. The inputs to the control logic gates come from two decoders, flip-flop and instruction register. The outputs of the control logic circuit are: signals to control the inputs of the registers, signals to control the read and write inputs of memory and signals to set, clear or complement the flip-flops. A step by step design technique has been proposed to design the control unit which connects all the proposed components with some other extra circuitry. The block diagram of the proposed control unit is shown in Fig. 8.

# ISSN No: 2348-4845 International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

Steps for control control unit:

(1) Construct a 3-to-8 decoder.

(2) Take the inputs of the 3-to-8 decoder from the instruction register (bit 12 to bit 15).

- (3) Construct a 4-bit sequence counter.

- (4) Construct a 4-to-16 bit decoder.

(5) Take the inputs of the 4-to-16 decoder from the outputs of the sequence counter.

(6) Construct a control logic gate.

(7) Take the inputs of the control logic gate from the instruction register (bit 0 to bit 11 and bit 15), 3-to-8 decoder (D0 to D7) and 4-to-16 decoder (T0 to T15).

(8) The outputs of the control register provide necessary signals to carry out the operation of the instruction register.

## Fig. 8. Proposed Reversible Control Unit

Fig. 9.Proposed reversible control gates associated with AR.

#### **E. Proposed Reversible Comparator:**

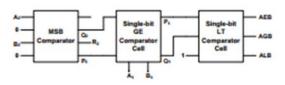

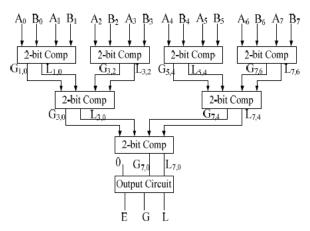

A magnitude comparator takes two numbers as input in binary form and determines whether one number is greater than, less than or equal to the other number. Comparators are used in central processing unit. We propose a compact and improved algorithm for constructing a compact reversible nbit binary comparator circuit. In order to improve the design, we use quantum cost minimization algorithm to design an nbit comparator. Reduction rules and algorithms are applied by template matching to minimize the quantum cost. The whole comparator is divided into three modules. They are as follows: We propose an MSB comparator circuit for comparing the nth bit (MSB) of two n-bit numbers. Then, a single-bit GE (greater or equal) comparator cell has been designed to generate greater and equal signal for the remaining (n-1) bits of two numbers with the previous comparison result of MSB. A single-bit LT (less than) comparator cell is designed to determine the less than signal. These three components with minimum quantum cost are then cascaded with each other using efficient techniques to design 2-bit and n-bit reversible binary comparators more compactly. A reversible 2bit binary comparator consists of a proposed reversible MSB comparator, a single-bit GE comparator and a single-bit LT comparator circuit. The reversible design of 2-bit binary comparator is shown in Fig. 10. The detail design of the individual blocks are not shown here due to space constraints.

Fig. 10. Proposed Reversible 2-bit comparator

The proposed reversible 8-bit comparator achieves the improvement in terms of number of gates, in terms of garbage outputs in terms of quantum cost, in terms of area and in terms of power over the existing best one [13].

International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

of Engineering,

Fig 11. Tree based 8-bit Comparator design

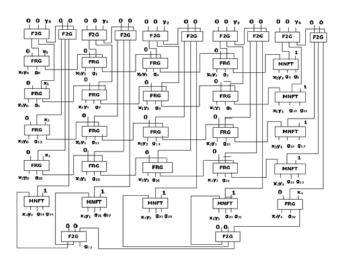

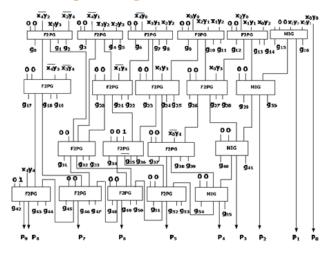

F. Proposed Reversible Multiplier Multiplier circuit is used in a processor. Multiplier circuit mainly has two components: Partial Product Generation (PPG) circuit and the Multi-Operand Addition (MOA) circuit. A multiplier circuit can be optimized in two ways. The algorithm of the multiplication can be optimized, as well as, the construction procedure of the PPG circuit and MOA circuit can be optimized. Firstly, we construct efficient template using reversible gates to reduce the quantum cost and delay. Secondly, we use an efficient searching technique to find the appropriate positions of different components of the proposed circuit. Finally, we propose two efficient algorithms which produce high speed minimum cost PPG circuit and MOA circuit of the proposed multiplier. The comparative study shows that the proposed reversible  $5 \times 5$  multiplier achieves the improvement in terms of number of gates, in terms of garbage outputs, in terms of quantum cost and in terms of constant inputs over the existing best one [14]. The proposed reversible  $n \times$ n multiplier requires n(2n - 1) gates, 4n(n - 1) + 1garbage outputs and 17n(n-1)+1 quantum cost; where as the best existing fault tolerant reversible multiplier [14] requires n(2n-1) + 5n/2 gates, 2n(n-1) garbage outputs and n(19n - 17) + 7 + 2n/2 quantum cost.

**ISSN No: 2348-4845**

Fig 12.5 5 fault tolerant reversible partial products generation circuit.

Fig 13.Circuit of 5 5 faulttolerant reversible signed multiplier.

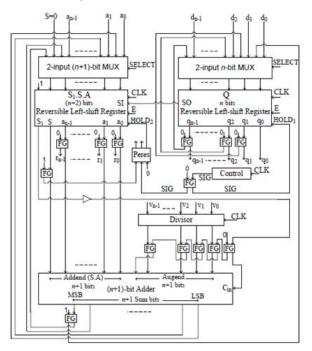

#### **G. Proposed Reversible Divider:**

Divider circuit is used in a processor. We propose two design techniques to construct reversible n-bit floating point nonrestoring division circuit. In the first approach of the reversible divider circuit, we propose carry propagate 2's complement adder and shifters. To speed up the division technique, we propose a major modification in the second approach of the reversible divider. We omit the carry propagation to avoid the propagation delay and introduce two new vectors and a single carry look-ahead adder circuit. Subtraction is implemented using 2's complement adder.

ISSN No: 2348-4845 International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

Both of the approaches can handle floating point numbers. Exhaustive search method is used to find the appropriate positions of reversible gates to obtain the minimum cost parameters for a specific function that are used to design the reversible divider circuit more compactly. The comparative study shows that the proposed reversible conventional 4-bit divider achieves the improvement in terms of number of gates, in terms of garbage outputs and in terms of quantum cost over the existing best one [15]. The proposed reversible high speed 4-bit divider achieves the improvement of in terms of number of gates, in terms of garbage outputs and in terms of quantum cost over the existing best one [15].

Figure 14. Proposed n-bit reversible division circuit

#### **IV. CONCLUSION:**

Hence, The reversible logic syntheses with the minimum cost factors are carried out for the components of the reversible processor. Many important contributions have been made in the literature towards the reversible implementations of arithmetic and logical structures; however, there have notbeen many efforts directed towards efficient approaches for designing reversible ALU (Arithmetic

Volume No: 3 (2016), Issue No: 6 (June) www.ijmetmr.com Logic Unit). Currently we are working on the design of the reversible ALU. We will propose an efficient approach to design the reversible ALU.Finally all the components of the reversible CPU (Central Processing Unit) are designed The proposed reversible CPU components can make a significant contribution in the field of low power reversible computing and quantum computing.

#### **REFERENCES:**

[1] C. H. Bennett, "Logical reversibility of computation," IBM J. Research and Development, vol. 17, pp. 525–532, 1973.

[2] D. P. DiVincenzo, "Quantum gates and circuits," Proceedings of the Royal Society of London A: Mathematical, Physical and Engineering Sciences, vol. 454, no. 1969, pp. 261–276, 1998.

[3] H. Axelsen, R. Glck, and T. Yokoyama, "Reversible machine code and its abstract processor architecture," in Computer Science Theory and Applications, ser. Lecture Notes in Computer Science. Springer Berlin Heidelberg, 2007, vol. 4649, pp. 56– 69.

[4] M. Thomsen, H. Axelsen, and R. Glck, "A reversible processor architecture and its reversible logic design," in Reversible Computation, ser. Lecture Notes in Computer Science. Springer Berlin Heidelberg, 2012, vol. 7165, pp. 30–42.

[5] M. Nielsen and I. Chuang, Quantum Computation and Quantum Information.Cambridge Univ. Press, 2000.

[6] Microwinddsch - schematic editor and digital simulator. [Online]. Available: http://www.microwind.net/dsch.ph

[7] Cmos 45 nm open cell library. [Online]. Available: http://www.si2.org/openeda.si2.org/projects/nangatelib

[8] L. Jamal, M. M. Alam, and H. M. H. Babu, "An efficient approach to design a reversible control unit of a processor," Sustainable Computing: Informatics and Systems, vol. 3, no. 4, pp. 286 – 294, 2013.

[9] A. S. M. Sayem and M. Ueda, "Optimization of reversible sequential circuits," Journal of Computing, vol. 2, no. 6, pp. 208 – 214, 2010.

[10] M. Polash and S. Sultana, "Design of a lut-based reversible field programmable gate array," Journal of computing, vol. 2, no. 10, pp. 103–108, 2010.

[11] M. Nachtigal and N. Ranganathan, "Design and analysis of a novel reversible encoder/decoder," in Nanotechnology (IEEE-NANO), 2011 11th IEEE Conference on, Aug 2011, pp. 1543–1546.

[12] M. Shamsujjoha and H. Babu, "A low power fault tolerant reversible decoder using mos transistors," in VLSI Design and 2013 12th International Conference on Embedded Systems (VLSID), 2013 26<sup>th</sup> International Conference on, Jan 2013, pp. 368–373.

[13] C. Vudadha, P. Phaneendra, V. Sreehari, S. Ahmed, N. Muthukrishnan, and M. Srinivas, "Design of prefix-based optimal reversible comparator," in VLSI (ISVLSI), 2012 IEEE Computer Society Annual Symposium on, Aug 2012, pp. 201–206.

[14] X. Qi, F. Chen, K. Zuo, L. Guo, and Y. L. M. Hu, "Design of fast fault tolerant reversible signed multiplier," International Journal of Physical Sciences, vol. 7(17), pp. 2506–2514, 2012.

[15] N. Nayeem, A. Hossain, M. Haque, L. Jamal, and H. Babu, "Novel reversible division hardware," in Circuits and Systems, 2009. MWSCAS '09.52nd IEEE International Midwest Symposium on, 2009, pp. 1134 –1138.