A Peer Reviewed Open Access International Journal

### Fine Grained CG using Stack Approach Integration of RTPG

Tellagorla Murali Krishna

Department of Electronics & Communication Engineering, Kommuri Pratap Reddy Institute of Technology, Hyderabad, Telangana 500039, India.

### ABSTRACT:

In Integrated circuits a gargantuan portion of chip power is expended by clocking system which comprises of timing elements such as flip flops, latches and clock distribution network. This paper enumerates power efficient design of shift registers using D flip flops along with Clock and Power gating integration. Clock gating and power gating proves to be very effective solutions for reducing dynamic and active leakage power respectively. The two techniques are coupled in such away that the clock gating information issued to drive the control signal of power-gating circuitry. In this paper, an activity driven fine-grained clock and power gating is proposed. First, a technique named Optimized Bus-Specific- Clock-Gating (OBSC) is introduced which reduces the problem of gated flip flop selection by appropriate selection of subset of flip flops. Then another technique named Run Time *Power Gating (RTPG) is proposed for power gating the* combinational logics performing redundant operations. The proposed shift registers are designed up to the layout level with 1V Power supply in 0.18um technology and simulated using micro wind simulations for different clock frequencies and the performance of the shift registers are evaluated by observing the average power.

Keywords: Optimized Bus-Specific-Clock- Gating (OBSC), RunTime Power Gating (RTPG), microwind.

### Introduction:

With the smaller geometries in Deep Sub-Micron (DSM) technology, the number of gates that need to be integrated on a single chip, power density, and total power are increasing rapidly. Also, designing for low-power has become increasingly important in a wide variety of applications. However, creating optimal low-

power designs involves trade such as timing versus power and are a versus power at the dierent stages of the design ow. Successful power-sensitive designs require engineers to have the ability to accurately and efficiently perform these trade.

To address these issues directly, it is essential to understand the different types and sources of power dissipation in digital Complementary Metal Oxide Semiconductor (CMOS) circuits. The reason for choosing the CMOS technology is that it is currently the most dominant digital IC implementation technology.

Power dissipation in CMOS digital circuits is categorized into two types: peak power and time-average d power consumption. Peak power is a reliability issue that determines both the chip life time and performance. The voltage drop e ects, caused by the excessive instantaneous current owing through the resistive power network, a\_ects the performance of a design due to the increased gate and interconnect delay. This large power consumption causes the device to overheat which reduces the reliability and life time of the circuit. Also noise margins are reduced, increasing the chance of chip failure due to crosstalk CMOS digital circuits occurs in two forms: dynamic and static. Dynamic power dissipation occurs in the logic gates that are in the process of switching from one state to another. During this process, any internal and external capacitance associated with the gate's transistors has to be charged, there by consuming power. Static power dissipation is associated within active logic gates (i.e., notcurrently switching from one state to another). Dynamic power is

**Cite this article as:** Tellagorla Murali Krishna, "Fine Grained CG using Stack Approach Integration of RTPG", International Journal & Magazine of Engineering, Technology, Management and Research, Volume 6 Issue 6, 2019, Page 15-20.

Volume No: 6 (2019), Issue No: 6 (June) www.ijmetmr.com

A Peer Reviewed Open Access International Journal

important during normal operation, especially at high operating frequencies, where as static power is more important during stand by, especially for battery-powered devices

For dynamic loss reduction we are using Clock Gating technique and for staticloss reduction we are suing RTPG technique explained below.

### **Clock Gating and Power Gating**

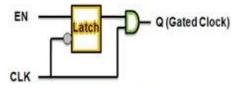

Clockgating isapopulartechniqueusedin many synchronouscircuitsforreducing dynamicpower dissipation. Clock gating saves power by adding more logic to а circuittoprunetheclocktree.Pruningthe clockdisablesportions ofthecircuitryso that theflipflopsin them do switchstates. not have to Switchingstatesconsumes power. Whennotbeing switched,the switchingpowerconsumptiongoes tozero, and onlyleakage currentsare incurred.<sup>[1]</sup>

Clockgating worksbytakingtheenable conditionsattached toregisters, and uses themtogate the clocks. Therefore it is imperative thatadesignmustcontainthese enable conditionsinorder touseandbenefit fromclockgating. Thisclockgating process can alsosavesignificantdieareaaswellas power, since it removes large numbers of muxes and replaces them with clock gating logic. This clock gating logicis generally intheformof"Integratedclock gating"(ICG)cells.However, clockgatinglogicwillchangetheclocktree notethatthe structure, since the clock gating logic will sit in the clock tree.

**Power** gating is а technique used in integrated circuitdesign to reducepowerconsumption, by currenttoblocksofthecircuitthatare shutting off the notinuse.Inadditiontoreducingstand-by orleakage power, powergating has the benefit of enablingIddq testing.

#### **Integrated Clock and Power Gating**

Clock GatingandPower Gatingare two most commonly used design methods to savedynamicandleakage power

> Volume No: 6 (2019), Issue No: 6 (June) www.ijmetmr.com

respectively.Howaboutintegrating thetwo solutionssuchthattheycomplement each other?Inthispost,I willtalkaboutasimple way to do so.

Clock Gating is accomplished by using ClockGatingIntegratedCell(CGIC)which gates theclocktothesequential elements present initsfanoutwhentheenablesignal

islogic0.PowerGatingstructuresmaybe of two types: Simple Power Gating andState RetentionPower Gating. Using the former technique,theoutputofthelogic gatesslowly leaksthechargeattheoutput andtherebywhenthe SLEEPsignalisdeasserted,onecannotpredictthelogicvalue

attheoutput.Thelattertechnique isableto retain thestateattheoutputwhichwaslast present before asserting theSLEEPsignal.

Let's take up a few plausible scenarios:

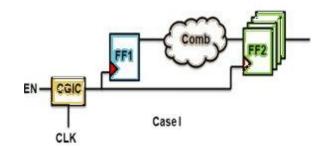

#### Case I

Normal Case: Whichemploys only conventional clockgating.Itisdepicted in the figure.

**Clock Gating Integrated Cell**

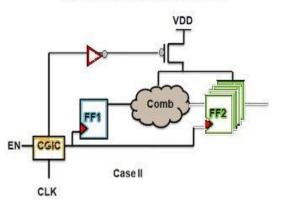

### Case II

Whenonedoesnotneedtoretain

thestatesofthecombinatorial cellsorthe sequential elements. One possiblescenario could be in the case of a standalone IP, whichisnotcomunicating withanyotherIP ontheSoC.Here onecanusetheesimple powergatingwhere

Case IIII

withother

**Case IV**

outputsneedtobe

couldbewhereonlythe

conventional flip-flops.

thepreviousvalue

domaincrossings.It

presentinthealways

the isolation cell

power supply!

"switchable

Whenboththecombinatorial

andthesequentialcellsinteract

Sinceitisaclassiccase of interaction

suchacase, isolation cellwould always

i.e., it would receive it's VDD supply

thealwaysONpowerdomainsupply. This

Whenonedoesnotneedtoretain

thestatesofthecombinatorial cells, but

byusingStateRetentionFlipFlopsinstead

### ISSN No: 2348-4845 International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

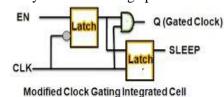

theSLEEPsignalis derivedfromtheCGICitselfusingalatch, asdepictedinthefigurebelow.Doingso, we wouldsavebothdynamicandleakage powers.

safe-stated.

the

sequentialoutputscommunicate

IPsontheSoC.Thiscanbeaccomplished

withother

can function only if receives the

power domain" with" always ON", it

neednotbe

entails the use of isolation cells between such power

isbecause, when the switchable power domain in OFF,

sequential

the

cells IPs.But

be

from

required.

Possibleuse-case

of

between

mustbenotedthatin

ONpowerdomain,

# Switchable Power Domain Isolation Cells

Isolation CellscanbesimplecellslikeAND oranORgate, whichreceiveoneinputina waythat, irrespective of the second input coming fromtheswitchablepowerdomain, the value would be controllable. For example,logic0forANDgate andlogic1 foranORgate.I willtrytotakethisupina separate post.

Here weclassified the shift register to three places

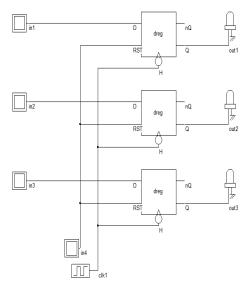

Fig: Non Clock Gating Circuit.

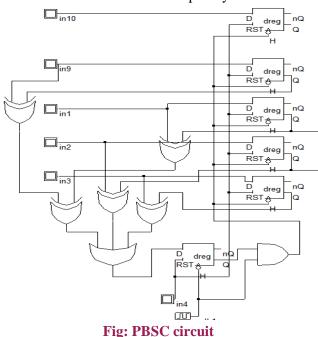

### PROPOSED OBSC

Optimized Bus Specific Clock Gating is very effective techniquetomaximize dynamic powerreductionas showninfig.3. It choosesonlyasubsetofflip-flops(FF)to be gated selectively,and theproblem of gatedFFselectionisreduced from exponentialcomplexity intolinear.It works by comparingtheinputsandoutputsand gatestheclockwhentheyare equal[11]. Considering

Volume No: 6 (2019), Issue No: 6 (June) www.ijmetmr.com

A Peer Reviewed Open Access International Journal

NFFsinthenon-CGcircuit, each FF can be chosen as gated or nongated. Hence,2NCGsolutionsare possibleand the exponential complexity problem is reduced intolinear. Assumethat alltheFFs thentheproblem arechosentobegatedinitially, isindeterminingwhich FFs shouldbeexcludedfromgating theFFwiththemaximum [1]. Heuristically, outputdatatoggle rateshouldbeexcluded from gating first. is because This that maximumoutputdata togglerateindicates thatminimumclocktoggles willbegated, thus power willreduce least or even increase iftheFFisgated.Moreformally,theFF with themaximumoutputtoggle rateis excludedfromgating first, then the FF with the second largest outputtoggle rate is excludedandsoon untilall theFFs are excluded(i.e., the original nonCGcircuit). Apparently, during the process of exclusion, therewillbeN+1possible CG solutions which is linear complexity.

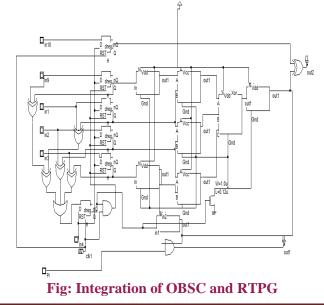

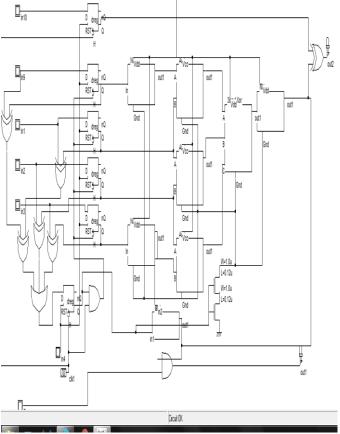

InordertoachieveintegrationofCGand RTPG. apply OBSC technique to the design, thenasubsetofFFsisclockgated. During theclockgated period, the outputs of the gated FFs are stable. Consequently, combinationallogicswhose those inputsonly dependongated FFoutputswillbeinactive and canbe power gatedasshown in Fig 6.(a).Foreachoutputof

> Volume No: 6 (2019), Issue No: 6 (June) www.ijmetmr.com

thepowergated cell, whether a connection to primary output presence hastobechecked.A holderlogic shouldbe addedinordertoavoidsignal floating. Suppose thatfouroutoffive FFs areclockgated. Thecircledcells are completely dependentonthe stablegated FF outputs, so they are notactiveandcanbe powergatedintosleep[1]. However,one inputof theXORgateiistheoutputof

ungatedFFA, and one input of the AND gate histheprimary input.Sinceboththe ungatedFFoutputandPI maynotbestable during the clock gated period, the XOR gate iandtheANDhmaybeactive. Sothey should not be order power gated. In to avoid floating signal, a holdershould be placed at theoutputofeachpowergated cell ifthat outputconnects tononpowergatedcellsor primary outputs (Pos)

If RTPGhastobeapplied, afooter(high-VthCMOStransistor)between theactual ground and virtual ground of the power gatedcellsshouldbeadded.After the integration of CG and RTPG, the low powerdesignshouldlooklikeFig.6 (b).The enable signalgenerated fromOBSCisused as thesleep signalfor thePG.The cells that aretotallydependenton gatedFFoutputs are power gated. Holdersare placed between thepowergatedcellsandthe nonpower gated cellssothatthenonpowergatedcells can function properly

A Peer Reviewed Open Access International Journal

If RTPGhastobeapplied, afooter(high-Vth CMOStransistor)between theactual ground and virtual ground of the power gatedcellsshouldbeadded.After the integration of CGand RTPG, the lowpower design shouldlooklikeFig.6 (b).Theenable signalgenerated fromOBSCisused as the sleep signalfor thePG.The cellsthatare totallydependenton gatedFFoutputsare gated. Holders areplaced between power the powergatedcells andthe nonpowergated cellssothatthenonpowergated cellscan function properly.

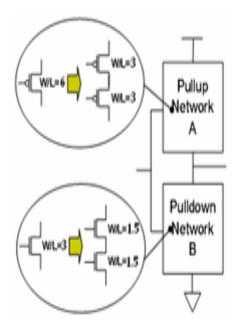

### Stack approach:

This is another new leakage reduction technique, which we call the stack approach.

## Fig: Structure ofvariablebodybiasing techniquewith sleep method

Another technique for leakage power reduction is thestack approach, which forces a stack effect by breakingdown an existing transistor into two half size transistors. When the two transistors areturned off together, induced reverse bias between the twotransistors results in sub-threshold leakage current reduction.However, divided transistors increase delay significantly and could limit the usefulness of the approach. It divides the w/l ratio into two equal parts.

Fig: Integration of OBSC and RTPG with Stack approach

### Tabulation

| Circuit             | Power Dissipaion |

|---------------------|------------------|

| Integration of OBSC | 0.305mW          |

| and RTPG with sleep |                  |

| Integration of OBSC | 0.163mW          |

| and RTPG with       |                  |

| Stack approach      |                  |

|                     |                  |

#### **Conclusion:**

In thisPaper,afine-grainedCGandRTPG integration isachievedinsequentialcircuits. First,anactivitydrivenfinegrained OBSC technique isevaluatedthatselects only a subsetofFFstogate.Moreover, theclock enable signalgeneratedintheOBSCcircuit canbeusedasthe

Volume No: 6 (2019), Issue No: 6 (June) www.ijmetmr.com

A Peer Reviewed Open Access International Journal

sleepsignalinRTPG. Following this,Sequentialcircuitsthat implementsbothOBSC andRTPGis considered andtheirperformances are evaluated withsleepandstack technique.

### **References:**

[1]LiLi,KenChoi,andHaiqing Nan, "Activity-Driven Fine-grainedClockGating andRunTimePower GatingIntegration", IEEEtransactionsonvery largescale integration(VLSI) systems,vol.21,no.8, August 2013.

[2] S.M.Kang,Y.Leblebici, Ed. , "CMOS DigitalIntegratedCircuitsanalysis and design". Third Edition, TMH, 2003

[3]M.MorrisMano,MichaelD.Ciletti,," Digital Design",FourthEdition,Pearson Education Inc

[4]ChristianPiguet,"LowpowerCMOSCircuits",Technology,LogicDesignandCADtools,Taylor andFrancis Group 2006"CAD

[5]J.S.Wang.P.H.Yang,"APulseTriggeredTSPCFFforHighspeed,LowpowerVLSIdesignApplications" IEEE, 1998

[6]NeilH.EWeste,KamranEshraghian, "Principles of CMOS VLSI Design," ASystemsPerspective,Second Edition,Pearson Education Inc ,2002

[7]K.Usamiand N.Ohkubo,"A design approach forfinegrainedrun-timepower gating using locally extracted sleep signals,"inProc.Int.Conf.Comput.Design, 2006, pp. 151–161

[8]L. Bolzani,A.Calimera,A.Macii,E. Macii, and M. Poncino, "Enabling concurrentclockandpower gatinginan industrialdesign flow,"inProc.Des.Autom. Test Eur. Conf., 2009, pp. 334–339

[9]K.Roy, S.Mukhopadkyay,andH. Mahmoodimeimand, "Leakage current mechanisms and leakage reduction techniques indeepsubmicrometer CMOS circuits," Proc. IEEE, vol. 91, no. 2, pp. 305-327,Feb. 2003.

[10]Y.Tsai,D.Duarte, N.Vijaykrishnan, and M.Irwin, "Characterizationand modeling of run-time techniques for leakage power reduction,"IEEE Trans. Very LargeScale Integr.(VLSI)Syst., vol. 12, no. 11, pp. 1221–1233, Nov. 2004.

[11]P.Babighian,L.Benini,andE.Macii,"AscalablealgorithmforRTLinsertionofgatedclocksbasedonODCscomputation,"IEEETrans.Comput.-AidedDesignIntegr.Circuits Syst., vol. 24, no.1, pp. 29–42, Jan. 2005.

[12] Andrew B.Kahng,SeokhyeongKang,BongilPark,"Active-Mode Leakage Reduction with Data-Retained Power Gating"Proc EDAA,2013

#### **Author Details**

#### Tellagorla Murali Krishna

Assistant Professor Department of Electronics & Communication Engineering, Kommuri Pratap Reddy Institute of Technology, Hyderabad, Telangana 500039, India.

Volume No: 6 (2019), Issue No: 6 (June) www.ijmetmr.com