A Peer Reviewed Open Access International Journal

# A Novel Architecture for Energy Efficient L2 Cache through Way Tag Information beneath Wright through Policy

# **M.Suresh**

Electronics and Communication Engineering, Swarnandhra College of Engineering and Technology, Narsapur.

#### J.E.N.Abhilash

Electronics and Communication Engineering, Swarnandhra College of Engineering and Technology, Narsapur.

# **M.Premchand**

Electronics and Communication Engineering, Swarnandhra College of Engineering and Technology, Narsapur.

# Abstract:

Numerous high-performance microprocessors utilize cache write-through policy for performance improvement and in the meantime accomplishing good tolerance to soft errors in on-chip caches. To cut back the memory access time cache is placed between the main memory and processor.

To diminish the soft errors in on chip caches and to enhance the performance, several processors utilize cache write through policy. In write through policy each write to the cache causes a write to main memory. The most discriminating issue in cache design is power dissipation. Way-tagged cache architecture is utilized to enhance the energy efficiency of write through caches.

In new technique, way tagged cache was utilized beneath write-through policy, it's consumed more energy. By maintaining the wag tag of L2 cache in the L1 cache during read operation. The proposed method empowers L2 cache to work in direct mapping manner during write hit and reducing tag comparison of cache miss prediction, if cache miss is predicted there is no need to access the L2 cache.

So that significant portion of energy will be reduced, without performance degradation. Simulation results are obtained both L1 and L2 cache configuration. The aimed technique achieves 70.7% energy saving in L2 cache on average with only 0.02% area overhead and no performance degradation, when compare with existent methods.

### **Keywords:**

Cache, Write-through policy, way tagged cache, Way-Tag buffer, low power.

### **I.INTRODUCTION:**

In superior microprocessors, constructions on chip cache systems are wide adopted. to stay knowledge in the cache memory and main memory identical, write-through and write-back policies area unit unremarkably used. Beneath the write-back policy, the data is written within the main memory only if the line is off from the cache. Whereas beneath the write-through policy, all the data/instruction is written each within the cache and within the main memory. The copy of knowledge in the main memory is rarely completely different from that of the copy in the cache [1]. As a result, the write-through policy maintains identical knowledge copies the least bit levels of the cache hierarchy throughout most of their life time of execution. Due to frequent access throughout write operations this allows giant energy overhead. a. Cache.

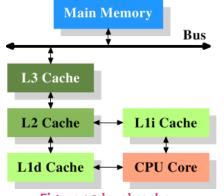

A CPU cache may be a cache utilized by the central processing unit (CPU) of a laptop to cut back the common time to access knowledge from the most memory. The cache may be a smaller, quicker memory that stores copies of the information from oft used main memory locations. Most CPUs have completely different freelance caches, as well as instruction and knowledge caches, wherever the information cache is typically organized as a hierarchy of additional cache levels (L1, L2 etc.)Think about a two-level (i.e., L1 and L2) cache system as an example. If the L1 knowledge cache implements the write-back policy, a write hit within the L1 cache ought not to access the L2 cache. In distinction, if the L1 cache is write through, so each L1 and L2 caches ought to be accessed for each write operation. Obviously, the write-through policy incurs additional write accesses within the L2 cache then L1 cache that successively will increase the energy consumption of the cache system.

Volume No: 2 (2015), Issue No: 3 (March) www.ijmetmr.com

A Peer Reviewed Open Access International Journal

therefore that power consumption is reduced as a result of power consumption is a one of the serious problems in coming up with cache system [2].

Figure 1.3 level cache

While facultative higher tolerance to soft errors, the write-through policy conjointly incurs giant energy overhead. This is often as a result of beneath the write-through policy, caches at the lower level expertise additional accesses throughout write operations. Think about a two-level (i.e., Level-1 and Level-2) cache system as an example. If the L1 information cache implements the write-back policy, a write hit within the L1cache doesn't have to be compelled to access the L2 cache.

In distinction, if the L1 cache is write-through, then each L1 and L2 caches have to be compelled to be accessed for each write operation. Obviously, the writethrough policy incurs additional write accesses within the L2 cache that successively will increase the energy consumption of the cache system. Power dissipation is currently thought of united of the important problems in cache style. Studies have shown that on-chip caches will consume concerning five hundredth of the whole power in superior microprocessors.

In this paper, the work is extending by creating the subsequent contributions. First, a close VLSI design of the planned approach labelled cache is developed, wherever varied style problems relating to temporal arrangement, management logic, in operation mechanisms, and space overhead [5]. Second, the concept of approach tagging is extended to several existing low-power cache style techniques, so higher trade-offs of performance and energy potency is achieved. Finally, a complete simulations is performed with new results covering the effectiveness of the planned technique beneath completely different cache configurations, any improve energy potency.

### **II.LITERATURE SURVEY:**

Many techniques are developed to cut back cache power dissipation. During this section, we have a tendency to shortly review some existing work associated with the planned technique. As per the fundamental plan of vertical cache partitioning was to optimize the capacitance of every cache access by increasing onchip cache hierarchy. Accessing a smaller cache has lower power consumption since a smaller cache features a lower load capacitance. Block buffering was AN example of this approach.

The block buffer itself is, in effect, another cache that is nearer to the processor than typical on -chip caches. equally the basic plan of the horizontal cache partitioning approach is to partition the cache knowledge memory into many segments. Every phase is battery-powered singly.

Cache sub-banking, planned in, is one horizontal cache partition technique that partitions the knowledge array of a cache into many banks. Every cache sub-bank is accessed singly. solely the cache sub-bank wherever the requested knowledge is situated consumes power in every cache access. Cache sub-banking saves power by eliminating excess accesses [4][7]. This but comes at the value of energy overhead.

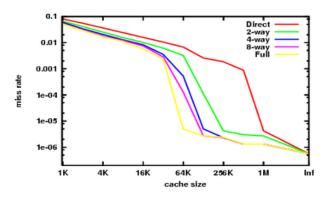

According to the system demand the cache will be designed as direct-mapping, four-way, two-way set associative with the necessary software package support. By accessing fewer tag and knowledge arrays, higher energy potency is earned. This technique is effectively appropriate for embedded system, however not appropriate for superior microprocessors.

Alternative techniques embrace way-predicting set-associative caches, planned by Inoue et al. That builds a prediction on the ways that of each tag and knowledge arrays during which the specified date can be situated in cache. If the prediction is correct, the corresponding means of information array is accessed to complete the operation. Otherwise, the remainder ways that of the cache area unit accessed to gather the specified knowledge.

# Architecture:

Volume No: 2 (2015), Issue No: 3 (March) www.ijmetmr.com

A Peer Reviewed Open Access International Journal

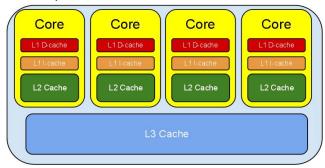

The event of caches and caching is one in every of the foremost important events within the history of computing. Nearly each fashionable computer hardware core from ultra-low power chips just like the ARM Cortex-A5 to the highest-end Intel Core i7 use caches. Even higher-end microcontrollers usually have tiny caches or provide them as choices [6]. The performance edges area unit too important to ignore, even in immoderate low-power styles. Fashionable system architectures have two or three levels within the cache hierarchy before planning to main memory. Usually the outer or Last Level Cache (LLC) are going to be shared by all cores on constant physical chip whereas the innermost area unit per core.

#### Figure 2. Intel EP processors

Figure 3. 2-level Architecture of cache

#### **Performance:**

The graph to the proper summarizes the cache performance seen on the number portion of the specification CPU2000 benchmarks, as collected by Hill and Cantin. These benchmarks square measure meant to represent the sort of employment that AN engineering pc} computer would possibly see on any given day [9]. The reader ought to detain mind that finding benchmarks that square measure even usefully representative of the many programs has been terribly troublesome, and there'll invariably be necessary programs with terribly totally different behavior than what's shown here.

Figure 4.Cache performance SPEC CPU2000

### **III.PROPOSED METHODOLOGY:**

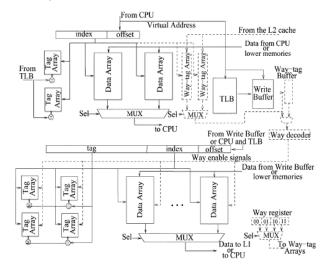

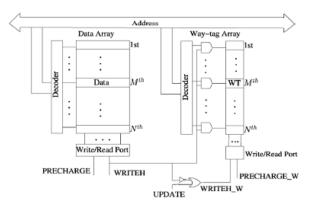

In this section we tackle our proposed way tag cache architecture. The following figure is our aimed way tag cache implementation.

#### Figure 5. Aimed way tag cache architecture

# Volume No: 2 (2015), Issue No: 3 (March) www.ijmetmr.com

A Peer Reviewed Open Access International Journal

In this proposed methodology we introduce several components like way-tag arrays, way-tag buffer, way decoder, and way register.

# **IV.WAY TAGGED CACHE IMPLEMENTATION:**

# Way tag array:

In the means -tagged cache, every cache line within the L1 cache keeps its L2 means tag data within the corresponding entry of the array. once an information is loaded from the L2 cache to the L1 cache, the means tag of this information is additionally written into the array.At a later time once change this information within the L1 information cache, the several copy in the L2 cache conjointly wants to be updated likewise. this is often primarily based over the write-through policy. The means tag hold on within the means -tag array is scan and passed to the way-tag buffer along with the information from the L1 information cache.

The write/read signal of way-tag arrays is generated from the write/read signal of the information arrays in the L1 information cache. an effect signal UPDATE is obtained from the cache controller. When the write access to the L2 information cache is caused by a L1 cache miss, UPDATE are declared and permits facultative the write operation to the way-tag arrays [8][9].

If a STORE instruction accesses the L1 information cache, UPDATE keeps invalid and write signal indicates a scan operation to the way-tag arrays. throughout the scan operations of the L1 cache, the way-tag arrays don't have to be compelled to be accessed and so square measure deactivated to cut back energy overhead.

Figure 6. way tag array

Volume No: 2 (2015), Issue No: 3 (March) www.ijmetmr.com

#### Table 1. way tag operation:

| Write | Update | Operation           |

|-------|--------|---------------------|

| 1     | 1      | Write way tag array |

| 1     | 0      | Read way tag array  |

| 0     | 0      | No access           |

| 0     | 1      | No access           |

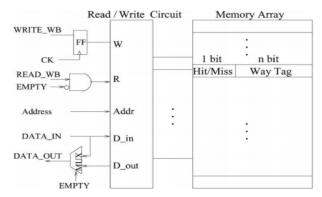

# Way tag buffer:

This quickly stores the manner tag reads from the manner tag array. It's a similar range of entries as the write buffer of l2 cache and the management signal is shared with it. Every entry of the manner tag buffer has n+1 bit. Wherever n is that the line size of manner tag arrays. associate degree further standing bit is there that shows whether or not the operation is within the current entry is a write miss on the l1 knowledge cameral the ways that of l2 cache have to be compelled to be activated once a write miss happens because the manner data isn't accessible. It's updated with the browse operations of manner tag arrays at a similar clock cycle [11].

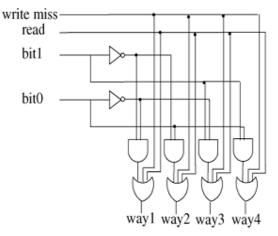

### Way decoder:

The method decryptr is used to decode the method tags and selects solely the correct method in the L2 cache. The method tag array of the line size is n=log 2 N bits. If there is write hit in the L2 cache the method decoder decodes the method tags and activates solely in a way. In L2 cache tag and knowledge arrays ar decoded by the method decoder and it is decoded at a similar time [10]. If there's write miss / scan miss in the L1 cache, all the ways

A Peer Reviewed Open Access International Journal

that of the L2 cache is ought to be elite. The operation mode of the method decoder is determined by the scan miss/write miss of the 2 signals. If the scan access is shipped to the L2 cache, then scan signal are going to be '1'.

#### Figure 8. way decoder

#### Way register:

Way register provides the way tags for the way tag array. in case of four way l2 cache labels "oo","o1","10","11" are stored in the way register and tagging in the l2 cache and the corresponding way tag is sent to way tag arrays. This operates under different modes during different kinds of operation.

### **V.RESULTANTS AND DISCUSSION:**

In this section, we tend to value the projected technique by comparison energy savings, space overhead, and performance with existing cache style techniques. Cache operates beneath totally different modes throughout browse and writes operations. solely the means containing the specified information is activated within the L2 cache for a write hit within the L1 cache, creating the L2 cache equivalently a direct-mapping cache to cut back energy consumption while not introducing performance overhead. electronic device is used to generate the alter signal for the tag arrays of the L2 cache. Once the standing bit indicates a write hit money supply outputs low to disable all the ways in which within the tag arrays. Electronic device chooses the output from the means decoder because the choice signals for the info arrays.

#### **Power Consumption:**

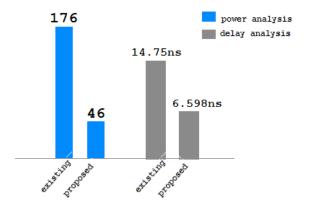

A selection of circuits have been enforced in zero.35micrometre technology to compare the projected GDI structure with existing alternatives, showing associate up-to seventy three.8% reduction in power in GDI as illustrated.

# **Delay thought:**

As portrayed within the table the herewith projected means -Tagged L2 cache design with economical information storage employs a discount in delay by 8.152nanoseconds as such, thence providing a discount within the power delay - product additionally.

# Table 2 analysis of power and delay

| Technique Used                                               | Parameter- Power Consumption(mW) |

|--------------------------------------------------------------|----------------------------------|

| Earlier cache architecture                                   | 176                              |

| Proposed Way-Tagged L2 Cache<br>with efficient datum storage | 46                               |

| Technique Used                                               | Parameter- Delay(ns)             |

| Earlier cache architecture                                   | 14.750                           |

| Proposed Way-Tagged L2 Cache<br>with efficient datum storage | 6.598                            |

#### **VI.CONCLUSION:**

This paper presents a brand new energy-efficient cache technique for superior microprocessors using the write-through policy. The planned technique attaches a tag to every manner within the L2 cache.

A Peer Reviewed Open Access International Journal

this manner tag is being sent to the way-tag arrays within the L1 cache once the information is loaded from the L2 cache to the L1 cache. Utilizing the manner tags hold on within the manner -tag arrays, the L2 cache will be accessed as a direct-mapping cache throughout the resultant write hits, thereby reducing cache energy consumption. The long run work is to use the partial manner tag within the manner tag array to boost the accuracy of cache miss and to scale back the tag comparisons of cache hit. This reduces tag comparison then the facility is consumed.

#### **REFERENCES:**

[1] T. Y. Ceiang and M. J. Hsiao, "Carry-select adder using single ripplecarry adder," Electron. Lett., vol. 34, no. 22, pp. 2101–2103, Oct. 1998.

[2] Y. He, C. H. Chang, and J. Gu, "An area efficient 64bit square rootcarry-select adder for lowpower applications," in Proc. IEEE Int. Symp.Circuits Syst., 2005, vol. 4, pp. 4082–4085.

[3] B. Ramkumar, H.M. Kittur, and P. M. Kannan, "ASIC implementation f modified faster carry save adder," Eur. J. Sci. Res., vol. 42, no. 1, pp.53–58, 2010.

[4] J. M. Rabaey, Digtal Integrated Circuits—A Design Perspective.Upper Saddle River, NJ: Prentice-Hall, 2001. [5] O. J. Bedrij, "Carry-select adder," IRE Trans. Electron. Comput., pp.340–344, 1962.

[6] Cadence, "Encounter user guide," Version 6.2.4, March 2008.8Youngjoon Kim and Lee-Sup Kim, "A Low Power Carry Select Adder With Reduced Area"

[7] Y. Kim and L.-S. Kim, "64-bit carry-select adder with reduced area,"Electron.Lett., vol. 37, no. 10, pp. 614–615, May 2001.

[8]. WESTE, N., and FSHRAGIAN, K.: 'PrinCipkSOf CMOS VLSI designs: a system perspectivc' (Addison-Weslcy, 1993), 2nd edn. p. 534

[9] N. Weste and K. Eshraghian, Principles of CMOS VLSI Design, ASystem Perspective. Reading, MA: Addison-Wesley, 1988, ch. 5.

[10] R. Zimmerman and W. Fichtner, "Low-power logic styles: CMOSversus pass-transistor logic," IEEE J. Solid-State Circuits, vol. 32, no.7, pp. 1079–1090, Jul. 1997.

[11] D. Radhakrishnan, "Low-voltage low-power CMOS full adder," IEEProc. Circuits Devices Syst., vol. 148, no. 1, pp. 19–24, Feb. 2001.