A Peer Reviewed Open Access International Journal

# Design and Performance Analysis of 1 bit Full Adder in 45nm Technology Using Multiplexer Based GDI Logic

A.Murali Associate Professor, Member IEEE, Department of ECE, Raghu Engineering College, Visakhapatnam, A.P, India. B.R.Chaitanya Raju

B.Tech (Pursuing), Department of ECE, Raghu Engineering College, Visakhapatnam, A.P, India.

### Abstract:

This paper proposes a new method for implementing a low power full adder by multiplexer based Gate Diffusion Input (GDI) and Pass Transistors using 90nm and 45nm technology. Full adder is a very common example of combinational circuits and is used widely in Application Specific Integrated Circuits. It is always advantageous to have low power action for the sub components used in VLSI chips.

The explored technique of realization achieves a low power high speed design for a widely used subcomponent full adder. Simulated outcome using state-of-art simulation tool shows power and speed comparison between conventional and proposed full adders also presented. All simulations have been performed on 90nm and 45nm standard models on Tanner EDA tool.

#### **Index terms:**

Conventional full adder, 2-Transistor GDI MUX, 18-TFA and PASS Transistor.

#### **1.INTRODUCTION:**

Most SOC design teams now regard power as one of their top design concerns

#### • Why low-power design?

i. Battery lifetime (especially for portable devices)ii. Reliability

### • Power consumption:

- i.Peak power

- ii. Average power

G.Navya Chandrika B.Tech (Pursuing), Department of ECE, Raghu Engineering College, Visakhapatnam, A.P, India.

#### **G.Siva Nagendra**

B.Tech (Pursuing), Department of ECE, Raghu Engineering College, Visakhapatnam, A.P, India.

#### **Low Power Strategies:**

• OS level : Partitioning, Power down

• Software level : Regularity, Locality and Concurrency

( Compiler technology for low power, instruction scheduling)

• Architecture level : Pipelining, Redundancy and Data Encoding

( ISA, architectural design, memory hierarchy, HW extensions, etc )

• Circuit/logic level : Logic styles, Transistor sizing and Energy recovery

(Logic families, conditional clocking, adiabatic circuits, asynchronous design)

• Technology level : Threshold reductions and multithreshold devices etc...

The challenge that has been faced by VLSI designers is to find effective techniques and their efficient applications to get minimum power dissipation without any compromise on their performance evaluation parameters. Thus, the design of low power circuits with improved performance is a major concern of modern VLSI designs.

The combination of certain logic styles and low power modules with low leakage circuit topologies may greatly reduce the limitations of deep-sub-micro-meter technologies. At the system level, in synchronous implementation of microprocessors, adder cells are the basic modules in a variety of arithmetic units such as arithmetic logical units, ripple carry adders , multipliers etc. Now a days, as growing applications, speed and portability are the major concerns of any smart device it demands small-size, low-power high

A Peer Reviewed Open Access International Journal

throughput circuitry. So, sub circuits of any VLSI chip needs high speed operation along with low-power consumption. So that logic circuits are designed using pass transistor logic techniques. [1]. It reduces the number of MOS transistors used in circuit, but it suffers with a major problem that output voltage levels is no longer same as the input voltage level. Each transistor in series has a lower voltage at its output than at its input.

### **II. RELATED WORK:**

#### A. CONVENTIONAL CMOS FULL ADDER:

The full adder operation[2] can be stated as follows: Given the three 1-bit inputs A, B, and Cin, it is desired to calculate the two 1-bit outputs Sum and Carry, where

# Sum = (A XOR B) XOR Cin

Cout = A AND B + Cin (A AND B)

Accordingly to the functions can be represented by CMOS logic as follows in fig 1

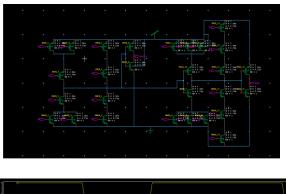

Fig1. Conventional 28-T 1 bit full adder

# TABLE I. TRUTH TABLE OF FULL ADDER

| A | B | Cin | Sum | Cout |

|---|---|-----|-----|------|

| 0 | 0 | 0   | 0   | 0    |

| 0 | 0 | 1   | 1   | 0    |

| 0 | 1 | 0   | 1   | 0    |

| 0 | 1 | 1   | 0   | 1    |

| 1 | 0 | 0   | 1   | 0    |

| 1 | 0 | 1   | 0   | 1    |

| 1 | 1 | 0   | 0   | 1    |

| 1 | 1 | 1   | 1   | 1    |

#### **B. 18TRANSISTOR LOGIC:**

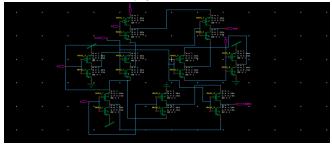

18T are used in the design. 10 Transistors are used to make five 2-1 multiplexer[3]. Among them four are used to generate Sum and one is used to generate Carry out. 4 transistors are used to invert A and B another 4 transistors are used to make AND and OR gate. All of the gates (except inverter) are designed with GDI technique where only two transistor are needed to construct any gate.

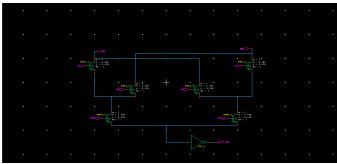

#### **C. PASS TRANSISTOR LOGIC:**

The basic difference of pass-transistor logic[4] compared to the CMOS logic style is that the source side of the logic transistor networks is connected to some input signals instead of the power lines. The advantage is that one pass-transistor network (either NMOS or PMOS) is sufficient to perform the logic operation, which results in a smaller number of transistors and smaller input loads.

#### **CARRY LOGIC:**

|  |             |  |  |          |  | • |

|--|-------------|--|--|----------|--|---|

|  |             |  |  |          |  |   |

|  | - Li Luz    |  |  |          |  |   |

|  |             |  |  |          |  |   |

|  | <b>لے</b> ا |  |  | <u>م</u> |  |   |

|  | ·=- b       |  |  |          |  |   |

|  |             |  |  |          |  |   |

A Peer Reviewed Open Access International Journal

#### **SUM LOGIC:**

#### **III. PROPOSD DESIGN USING 45nm TECH:**

The basic architecture of the 2:1 MUX using GDI method is shown in fig 1. In this configuration we have connected PMOS and NMOS gate along with a SEL line 'A', as in MUX. As we know that PMOS works on ACTIVE LOW and NMOS works on ACTIVE HIGH. So, when the SELECT input is low (0) then the PMOS get activated, and show the input 'B' in the output and due to low input (0) the NMOS stands idle, as it is activated in high input. Same for the case, while the G input is high (1) then the NMOS get activated, and show the input 'C' at the output. Thus this circuitry behaves as a 2-input MUX using 'A' as SEL line, and shows the favourable output as 2:1MUX. Now it's implemented the low power full adder circuit with the help of 2T MUX, made by GDI technique. It require total 6 numbers of 2T MUX having same characteristics to design a 12T full adder[6].

#### A. Gate Diffusion Input Technique:

The GDI technique offers realization of extensive variety of logic functions using simple two transistor based circuit arrangement. This scheme is appropriate for fast and low power circuit design, which reduces number of MOS transistors as compared to CMOS and other existing low power techniques, while the logic level swing and static power dissipation improves. GDI technique based full adder have advantages over full adder using pass transistor logic or CMOS logic and is categorized by tremendous speed and low power. The technique has been described below

1. The GDI cell consists of one nMOS and one pMOS. The structure looks like a CMOS inverter. Though in case of GDI both the sources and corresponding substrate terminals of transistors are not connected with supply and it can be randomly biased.

2. It has three input terminals: G (nMOS and pMOS shorted gate input), P (pMOS source input), and N (nMOS source input). The output is taken from D (nMOS and pMOS shorted drain terminal) [11].

#### **B. Logic Analysis:**

The digital circuit [5] can be analyzed logically with the help of simple Boolean algebra. The outputs of each MUX can be analyzed to get the sum & carry.

A Peer Reviewed Open Access International Journal

$\begin{array}{l} \text{MUX1=} (B\overline{A}+CA) \\\\ \text{MUX2=} (C\overline{A}+BA) \\\\ \text{MUX3=} [(C\overline{A}+BA)\overline{C}+(B\overline{A}+CA)C] \\\\ = AB\overline{C}+\overline{A}BC+AC \\\\ = AB\overline{C}+\overline{A}BC+AC \\\\ = AB\overline{C}+\overline{A}BC+AC(B+\overline{B}) \\\\ = AB\overline{C}+\overline{A}BC+ABC+A\overline{B}C \\\\ = AB\overline{C}+ABC+\overline{A}BC+ABC+A\overline{B}C \\\\ = AB(C+\overline{C})+BC(A+\overline{A})+AC(B+\overline{B}) \\\\ = AB+BC+CA=Cout \\\\ \text{MUX4=} \overline{A}\overline{B}+(\overline{A}B+AC)B \\\\ \text{MUX5=} (C\overline{A}+BA)\overline{B}+AB \\\\ \text{MUX5=} (C\overline{A}+BA)\overline{B}+AC \\\\ \text{MUX5=} [\overline{A}\overline{B}+(\overline{A}B+AC)B]\overline{C}+[(C\overline{A}+BA)\overline{B}+AB]C \\\\ = A\overline{B}\overline{C}+\overline{A}B\overline{C}+\overline{A}\overline{B}C+ABC=A \ \oplus B \ \oplus C=Sum \\\\ \text{Logic transition, short-circuit current and leakage} \end{array}$

current are the three main sources of power dissipation in CMOS VLSI circuits [6], [7]. During the transition of output from one logic level to other both the NMOS and PMOS transistors become active and provides a short circuit path directly between supply to ground which increases the power consumption of the circuit. As the proposed 12-T full adder is made of GDI based MUX, it does not provide direct connections between supply and ground, so the probability of a getting short circuit current during switching can be considerably reduced; i.e, the power consumption due to short circuit current is considerably small. Again, in the proposed 12T full adder, all the select line of the MUX i.e. the G nodes of the GDI cells are directly connected with the input signals, results a much faster transition (less delay) in its output signals. As a result, the power consumption of the final pad out stage is low and it can provide faster Sum and Cout outputs.

# **C. POWER CONSUMPTION:**

There are three main components of power consumption in digital VLSI circuits.

# i. Switching component:

consumed in charging and discharging of the circuit capacitances during transistor switching.

# ii. Short-circuit component:

Created by short-circuit current flowing from supply voltage to ground during transistor switching.

Volume No: 3 (2016), Issue No: 3 (March) www.ijmetmr.com

### iii. Static power component:

Existence of static and leakage currents in stable state of circuit cause this component of power consumption. The first two components are referred to as dynamic power, since power is consumed dynamically while the circuit is changing states [8]. Dynamic power accounts for the majority of the total power consumption in digital VLSI circuits The average power dissipation for a CMOS circuit is given by Pavg = Pdynamic+ Pshort circuit + Pstatic ......(1) = Vdd .fclk . $\Sigma$ (Vi swing .Ci load .  $\alpha$ i ) + Vdd. $\Sigma$ Ii sc +Vdd. II .

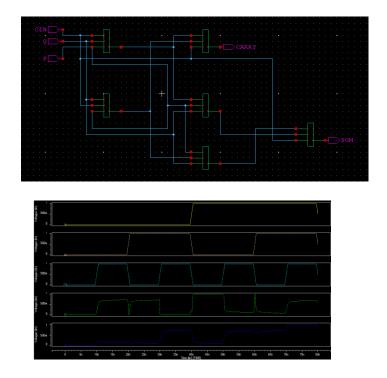

### **IV. SIMULATIONS AND COMPARISIONS:**

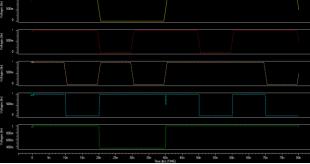

In order to test the performance of proposed adder cells, all schematic have performed on Tanner EDA tool version 13.0v and Simulations have carried out using HSPICE to measure the power consumption, propagation delay and power delay product of the full adders using 90nm and 45nm technology with same input conditions of 1.0 V 0.7V supply and the maximum frequency of 100 MHz. Simulation results are shown in figures.

# **Propagation Delay Analysis**

March 2016

A Peer Reviewed Open Access International Journal

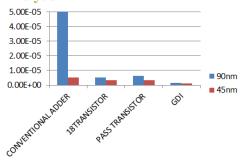

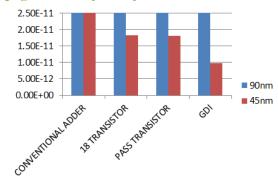

# Comparison tables with Conventional Full Adder using 90nm and 45nm Technologies

| 90nm TECHNOLOGY    | POWER        | DELAY    | PDP         | TRANSISTOR<br>COUNT |

|--------------------|--------------|----------|-------------|---------------------|

| CONVENTIONAL ADDER | 15.8 mW      | 20.02 ns | 319.16pJ    | 28                  |

| 18 TRANSISTOR      | 5.365E-03 mW | 5.970 ns | 32.02E-03pJ | 18                  |

| PASS TRANSISTOR    | 6.325E-03 mW | 0.776 ns | 4.90E-03 pJ | 16                  |

| GDI                | 1.335E-03 mW | 0.252ns  | 0.33E-03 pJ | 12                  |

| 45nm TECHNOLOGY       | POWER   | DELAY     | PDP          | TRANSISTOR<br>COUNT |

|-----------------------|---------|-----------|--------------|---------------------|

| CONVENTIONAL<br>ADDER | 5.25 uW | 0.298 ns  | 15.64E-04 pJ | 28                  |

| 18 TRANSISTOR         | 3.37 uW | 0.0185ns  | 6.143E-05 pJ | 18                  |

| PASS TRANSISTOR       | 3.25 uW | 0.0180 ns | 5.866E-05 pJ | 16                  |

| GDI                   | 1.18 uW | 0.0097 ns | 11.54E-06 pJ | 12                  |

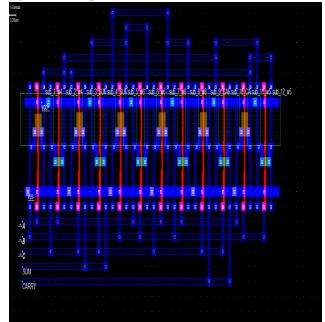

# Layout of Proposed Adder Cell

#### VII. CONCLUSION:

From the above results it can be concluded that 1 bit CMOS full adder designs has got better performance in delay, power and area consideration in comparison with conventional full adder. It shows that in contrast to other conventional techniques, this approach is better and it will be more appropriate for industrial practice in complex process technologies.

# **ACKNOWLEDGMENT:**

We express my deep sense of gratitude and thanks Chairman sir Sri. Raghu Kalidindi, Dean Prof S. Veerabhadraiah, Head of the Department Mr. K.Phaninder Vinay and Principal Dr. R.Kameswara Rao sir of Raghu Engineering College Visakhapatnam, India for giving us this opportunity to carry out my project work at highly esteemed Organization.

### **REFERENCES:**

[1]Biswarup Mukherjee, Aniruddha Ghosal, "Design & Study of a Low Power High Speed Full Adder Using GDI Multiplexer" IEEE 2nd International Conference on Recent Trends in Information Systems (ReTIS), IEEE, 2015, page 465-470.

[2]Jaume Segura, Charles F. Hawkins CMOS electronics: how it works, how it fails, Wiley-IEEE, 2004, p age 132.

[3]International Journal of Computer Applications (0975 – 8887 " Analysis of Various Full-Adder Circuits in Cadence" Page 30-37.

[4]Yano, K, et al, "A 3.8 ns CMOS 16\*16b multiplier using complementary pass transistor logic", IEEE J. Solid State Circuits, Vol 25, p388-395, April 1990.

[5]Clive Maxfield Bebop to the Boolean boogie: an unconventional guide to electronics Newnes, 2008, pp. 423-426.

[6]Yingtao Jiang, Abdulkarim Al-Sheraidah, Yuke Wang, Edwin Sha, and Jin-Gyun Chung, "A Novel Multiplexer-Based Low-Power Full Adder" IEEE Transaction on circuits and systems-II: Express Brief, Vol. 51, No. 7,p-345, July- 2004.

[7]Makoto Suzuki, et al, "A 1.5 ns 32 b CMOS ALU in double pass transistor logic", ISSCC Dig. Tech. Papers, pp 90-91, February 1993.

A Peer Reviewed Open Access International Journal

[8]N. Ohkubo, et al, "A 4.4 ns CMOS 54X54 b multiplier using pass transistor multiplexer", Proceedings of the IEEE 1994 Custom Integrated Circuit Conference, May 1-4 1994, p599-602, San Diego, California.

[9]Mohamed W. Allam, "New Methodologies for Low-Power High- Performance Digital VLSI Design", PhD. Thesis, University of Waterloo, Ontario, Canada, 2000. [10]A.Bazzazi and B.Eskafi, "Design and Implementation of Full Adder Cell with the GDI Technique Based on 0.18µm CMOS Technology", International Multi Conference of Engineers and Computer Scientists (IMES) Vol II, March 17 - 19, 2010, Hong Kong.

[11] Arkadiy Morgenshtein, Alexander Fish, and Israel A. Wagner, "Gate- Diffusion Input (GDI): A Power-Efficient Method for Digital Combinatorial Circuits", IEEE Transaction on VLSI Systems, Vol. 10