A Peer Reviewed Open Access International Journal

# A Novel Transformerless PV Inverter with Reduced Leakage Current and Effective Control

#### **Ankuri Umarani**

Department of EEE,

VIF College of Engineering & Technology,

Moinabad Mandal, Hyderabad, Telangana – 500075,

India.

#### **Abstract:**

Three-phase transformerless inverter is widely used in low-power photovoltaic (PV) grid-connected systems due to its small size, high efficiency and low cost. When no transformer is used in a grid connected photovoltaic (PV) system, a galvanic connection between the grid and PV array exists. In these conditions, dangerous leakage currents (commonmode currents) can appear through the stray capacitance between the PV array and the ground. The former, in order to create a galvanic isolation between the input and the output include a transformer (mandatory in some countries) that limits the whole system performances in terms of efficiency, weight, size and cost. On the contrary, transformerless inverters do not present any isolation and are characterized by little size, lower cost and higher efficiency (more than 2% higher).

Nevertheless, the lack of transformers leads to leakage currents that can be harmful to the human body, as well as for the whole conversion system integrity. In order to minimize the ground leakage current and improve the efficiency of the converter system, transformerless PV inverters utilizing unipolar PWM control. In this project it presents a high-reliability single-phase transformerless grid-connected inverter that operate super junction MOSFETs to accomplish high efficiency for photovoltaic applications. In this paper proposed converter tested for the three phase system and it is analyzed. kept constant at midpoint of dc input voltage, results low leakage current. Finally, to validate the proposed topology, a 1 kW laboratory prototype is built and tested.

#### **Tajvar Sultana**

Department of EEE,

VIF College of Engineering & Technology,

Moinabad Mandal, Hyderabad, Telangana – 500075,

India.

The experimental results show that the proposed topology can inject reactive power into the utility grid without any additional current distortion and leakage current. The maximum efficiency and European efficiency of the proposed topology are measured and found to be 98.54% and 98.29%, respectively recently, the photovoltaic power generation system has been focused as one of the most significant energy sources due to the rising concern about global warming, and the increase of electrical power consumption. In addition, the PV module has no moving parts, which have made it very robust, long lifetime and low maintenance device. Though the PV module is still expensive, but due to the large-scale manufacturing it has become increasingly cheaper in the last few years.

It has been reported that the milestone of 100GW installed PV power all over the world was achieved at the end of 2012 and increased to 140GW at the end of 2013, and the majority were grid connected. Therefore, a prediction has been made that the future grid tied PV system will play an important role in the regulation of the conventional power system. The proposed transformer less inverter topologies consisting of six MOSFET switches (S1-S6) and six diodes (D1-D6). L1A, L1B, L2A, L2B, L1g, L2g and Co make up the LCL type filter connected to the grid. VPV and Cdc represent the input dc voltage and dc link capacitor.

Cite this article as: Ankuri Umarani & Tajvar Sultana, " A Novel Transformer LESS PV Inverter with Reduced Leakage Current and Effective Control", International Journal & Magazine of Engineering, Technology, Management and Research, Volume 4 Issue 11, 2017, Page 202-211.

A Peer Reviewed Open Access International Journal

The proposed topology is derived from the topology presented to overcome the low reverse-recovery issues of MOSFETs body-diode when injects reactive power into the utility grid. Therefore, the proposed topology can be implemented with MOSFET switches without reliability and efficiency penalty. The proposed topology can also employ unipolar-SPWM with three-level output voltage.

#### **Index Terms:**

Common mode, converter, high efficiency, leak-age current, reactive power, transformerless.

#### **INTRODUCTION:**

In recent past years the photovoltaic (PV) systems have been received unprecedented concentration due to the raise of concerns about adverse effects of extensive use of fossil fuels on the environment and energy utilization with security in grid-connected PV systems that are still outnumbered by the power generation schemes which are based on oil or natural gas or coal or nuclear or hydro or wind or any combination of these [1] PV systems capacity is majorly based on the order of tens of megawatts that have been installed and interfaced at the grid level in the primary distribution where the PV system installation at the secondary distribution level are dominated by rooftop units with distinct capacities on the order of a few kilowatts with no significant impact on the existing power systems.

An attractive feature of PV systems is that they produce electric power without harming the environment, by directly transforming a free unlimited source of energy, solar radiation, into electricity. This fact along with the continuing decrease in PV arrays cost and the increase in their efficiency has resulted in the use of PV generation systems. In the past, PV sources were commonly used in isolated and standalone applications. Nowadays, the trend is to connect the PV systems to the public grid, selling the generated power with advantageous price ratings fixed by governmental policies.

High frequency common-mode (CM) voltages must be avoided for a transformerless PV gridconnected inverter because it will lead to a large charge/discharge current partially flowing through the inverter to the ground. This CM ground current will cause an increase in the current harmonics, higher losses, safety problems, and electromagnetic interference (EMI) issues For a grid-connected PV system, energy yield and payback time are greatly dependant on the inverter's reliability and efficiency, which are regarded as two of the most significant characteristics for PV inverters. In order to minimize the ground leakage current and improve the efficiency of the converter system, transformerless PV inverters utilizing unipolar PWM control have been presented [8]-[10]. The weighted California Energy Commission (CEC) or (EU) efficiencies of European Union commercially available and literature-reported singlephase PV transformerless inverters are in the range of The reported system peak and CEC efficiencies with an 8kW converter system from the product datasheet is 98.3% and 98%, respectively, with 345-V dc input voltage and a 16kHz switching frequency.

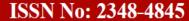

However, this topology has high conduction losses due to the fact that the current must conduct through three switches in series during the active phase. Another disadvantage of the H5 is that the linefrequency switches S1 and S2 cannot utilize MOSFET devices because of the MOSFET body diode's slow reverse recovery. Replacing the switch S5 of the H5 inverter with two split switches S5 and S6 into two phase legs and adding two freewheeling diodes D5 and D6 for freewheeling current flows, the H6 topology was proposed in [10]. The H6 inverter can be implemented using MOSFETs for the line frequency switching devices, eliminating the use of less efficient IGBTs. The reported peak efficiency and EU efficiency of a 300 W prototype circuit were 98.3% and 98.1%, respectively, with 180 V dc input voltage and 30 kHz switching frequency.

A Peer Reviewed Open Access International Journal

The fixed voltage conduction losses of the IGBTs used in the H5 inverter are avoided in the H6 inverter topology improving efficiency; however, there are higher conduction losses due to the three seriesconnected switches in the current path during active phases. The shootthrough issues due to three active switches series connected to the dc-bus still remain in the H6 topology. Another disadvantage to the H6 inverter is that when the inverter output voltage and current has a phase shift the MOSFET body diodes may be activated. This can cause body diode reverse-recovery issues and decrease the reliability of the system.

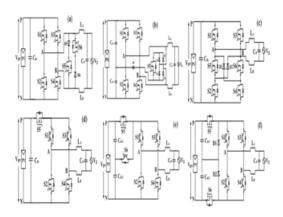

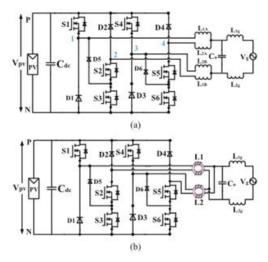

Fig1. Single-phase transformerless PV inverters using super junction MOSFETs: (a) H5, (b) H6, and (c) dualparalleled-buck inverters

Another high-efficiency transformer less MOSFET inverter topology is the dual-paralleled-buck converter, as shown in Fig. 1(c). The dual-parallel-buck converter was inversely derived from the dual-boost bridgeless power factor correction (PFC) circuit in [2]. The dual-paralleled buck inverter eliminates the problem of high conduction losses in the H5 and H6 inverter topologies

because there are only two active switches in series with the current path during active phases. The reported maximum and EU efficiencies of the dualparalleled-buck inverter using Cool MOS switches and SiC diodes tested on a 4.5 kW prototype circuit were 99% and 98.8%, respectively, with an input voltage of 375 V and a switching frequency at 16 kHz. The main issue of this topology is that the grid is directly connected by two active switches S3 and S4, which may cause a grid short-circuit problem, reducing the reliability of the topology. A dead time of 500 µs between the linefrequency switches S3 and S4 at the zero-crossing instants needed to be added to avoid grid shoot-through. This adjustment to improve the system reliability comes at the cost of high zero-crossing distortion for the output grid current. One key issue for a high efficiency and reliability transformerless PV inverter is that in order to achieve high efficiency over a wide load range it is necessary to utilize MOSFETs for all switching devices Another key issue is that the inverter should not have any shoot-through issues for higher reliability.

In order to address these two key issues, a new inverter topology is proposed for single-phase transformerless PV grid-connected systems in this paper. The proposed transformerless PV inverter features: 1) high reliability because there are no shootthrough issues, 2) low output ac current distortion as a result of no dead-time requirements at every PWM switching commutation instant as well as at grid zero-crossing instants, 3) minimized CM leakage current because there are two additional ac-side switches that decouple the PV array from the grid during the freewheeling phases, and 4) all the active switches of the proposed converter can reliably employ super junction MOSFETs since it never has the chance to induce MOSFET body diode reverse recovery. As a result of the low conduction and switching losses of the superjunction MOSFETs, the proposed converter can be designed to operate at higher switching frequencies while maintaining high system efficiency.

A Peer Reviewed Open Access International Journal

Higher switching frequencies reduce the ac-current ripple and the size of passive components.

#### **Wind Energy and Wind Power:**

Wind is a form of solar energy. Winds are caused by the uneven heating of the atmosphere by the sun, the irregularities of the earth's surface, and rotation of the earth. Wind flow patterns are modified by the earth's terrain, bodies of water, and vegetative cover. This wind flow, or motion energy, when "harvested" by modern wind turbines, can be used to generate electricity.

#### **How Wind Power Is Generated:**

The terms "wind energy" or "wind power" describe the process by which the wind is used to generate mechanical power or electricity. Wind turbines convert the kinetic energy in the wind into mechanical power. This mechanical power can be used for specific tasks (such as grinding grain or pumping water) or a generator can convert this mechanical power into electricity to power homes, businesses, schools, and the like.

Fig 2.Wind turbines

## II. PROPOSED TOPOLOGY AND OPERATING PRINCIPLE:

#### A. Structure of the Proposed Topology:

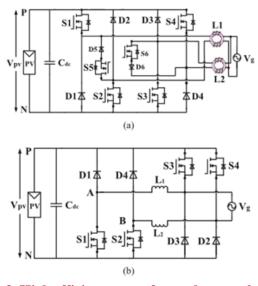

Fig. 4 shows the proposed transformerless inverter topolo-gies consisting of six MOSFET switches (S1-S6) and six diodes (D1-D6).  $L_{1A}$ ,  $L_{1B}$ ,  $L_{2A}$ ,  $L_{2B}$ ,  $L_{1g}$ ,  $L_{2g}$  and  $C_o$  make up the LCL type filter connected to the grid.  $V_{PV}$  and  $C_{dc}$  represent the input dc voltage and dc link capacitor. The proposed topology is derived from the topology presented in Fig. 2(c) to overcome the low reverse-recovery issues of MOSFETs body-diode when injects reactive power into the utility grid. Therefore, the pro-posed topology can be implemented with MOSFET switches without reliability and efficiency penalty. The proposed topol-ogy can also employ unipolar-SPWM with three-level output voltage.

#### **B.** Operating Principle of the Proposed Topology:

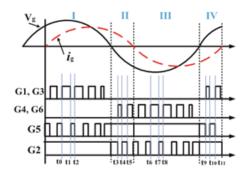

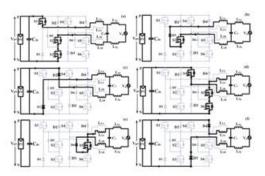

The switching pattern of the proposed topology is shown in Fig. 5, where G1, G2, G3, G4, G5, and G6 represent the gate drive signals of the switches S1, S2, S3, S4, S5, and S6, respec-tively. The operation principle of the proposed topology within a grid period is divided into four regions as shown in Fig. 5. Due to the symmetry of the operation of the positive and negative half cycle of grid current, here only positive half cycle explanation is given. However, the circuit diagram for negative half cycle operation is depicted in Fig. 6.

#### **Region I:**

In this region, both the grid current and voltage are positive. During the period within this region, S2 is always on,

A Peer Reviewed Open Access International Journal

Fig. 2. Some existing transformerless topologies for grid-tied PV system using MOSFETs as main power switches

Fig. 3. High efficiency transformerless topology

while S1 & S3 synchronously and S5 complementary commu-tate with switching frequency. There are always two states that generate the output voltage of +V<sub>PV</sub> and 0. State 1(t0:t1): At t = t0, the switches S1 & S3 are turned-on and the inductor current increases through grid as shown in Fig. 6(a). In this state, the voltages  $V_{1N}$  and  $V_{2N}$  can be defined as:  $V_{1N} = +V_{P\ V}$  and  $V_{2N} = 0$ , thus the inverter output voltage  $V_{12} = (V_{1N} - V_{2N}\ ) = +V_{P\ V}\$ . State 2(t1:t2): When the switches S1 and S3 are turned-off, the inductor current freewheels through S2 and D5. In this state,  $V_{1N}$  falls and  $V_{2N}$  rises until their values are equal. Therefore,

the voltages  $V_{1N}$  and  $V_{2N}$  becomes:  $V_{1N} = V_{P \ V} \ / 2$  and  $V_{2N} = V_{P \ V} \ / 2$  and the inverter output voltage  $V_{12} = 0$ .

#### **Region II:**

In this region, the inverter output voltage is nega-tive, but the current remains positive. During the period of this region, S5 is always on, while S4 & S6 synchronously and S2.

Fig. 4. (a) Circuit structure of the proposed transformerless topology for grid-tied PV system (b) circuit structure with coupled inductor.

Fig. 5. Switching pattern of the proposed topology with reactive power flow.

complementary commutate with switching frequency. There are also two states that generate the output voltage of  $-V_{PV}$  and 0.

State 3(t3:t4): In this state, the switches S4 and S6 are turned-on and the filter inductors are demagnetized.

A Peer Reviewed Open Access International Journal

Since the inverter output voltage is negative and the current remains.

Fig. 6. The operating principle of the proposed topology: (a) state 1 (b) state 2 (c) state 3 (d) state 4 (e) state 5 (f) state 6.

positive; therefore, the inductor current is forced to freewheel through the diode D1 and D2, and decreases rapidly for enduring the reverse voltage as shown in Fig. 6(c). The voltages V1N and V2N can be defined as: V1N =0and V2N =+VPV, thus the inverter output voltage V12 =(V1N -V2N)=-VPV. State 4(t4:t5): At t = t4, the switches S4 and S6 are turnedoff and S2 is turned-on. Therefore, the inductor current flows through S2 and D5 like as state 2 (Fig. 6(b) can be referred as equivalent circuit). This state is called as energy storage mode. ThevoltagesV1N andV2N couldbe:V1N = VPV/2andV2N = VPV/2, and thus the inverter output voltage, V12 =0

# III. HIGH FREQUENCY CM MODEL OF THE PROPOSED TOPOLOGY FOR LEAKAGE CURRENT ANALYSIS:

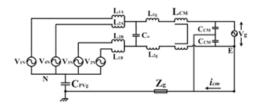

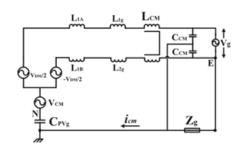

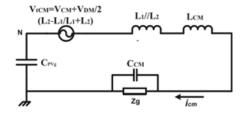

The PV module generates an electrically chargeable surface area which faces a grounded frame. In case of such configuration, a capacitance is formed between the PV module and the ground. Since this capacitance occurs as an undesirable side effect, it is referred as parasitic capacitance. Due to the loss of galvanic separation between the PV module and the grid, a CM resonant circuit can be created. An alternating CM voltage that depends on the topology structure and control scheme, canelectrify the resonant circuit and may lead to higher ground leakage current [6], [10]. In

order to analyze the CM characteristics, an equivalent circuit of the proposed topology as shown in Fig. 7 can be drawn, where V1N,V2N,V3N and V4N are the controlled voltage source connected to the negative terminal N, LCM and CCM are the CM inductor and capacitor, CPVg is the parasitic capacitance, and Zg is the grid impedance. During the positive half-cycle, the switches S4 and S6 are always off. As a result, the controlled voltage sources V3N and V4N are zero and can be removed. According to the definition of common-mode and differential-mode voltage:

$$V_{CM} = \frac{1}{2} \left( V_{1N} + V_{2N} \right) \tag{1}$$

$$V_{DM} = V_{1N} - V_{2N} (2)$$

Solving (1) and (2), V1N and V2N can be expressed as follows:

Fig. 7. Equivalent CM model of the proposed topology.

Fig. 8. Simplified CM model at switching frequency for positive half cycle.

Fig. 9. Simplified single loop CM model

A Peer Reviewed Open Access International Journal

$$V_{1N} = V_{CM} + \frac{1}{2}V_{DM} \tag{3}$$

$$V_{2N} = V_{CM} - \frac{1}{2}V_{DM} \tag{4}$$

In order to illustrate the CM model at switching frequency, equation (3) and (4) could be replaced for the bridge-leg in Fig. 7. The grid is a low frequency (50–60 Hz) voltage source; thus the impact of grid on the leakage current can be neglected [3]. The DM capacitor Co can also be removed since it has no effect on the leakage current. Consequently, the simplified high frequency CM model of the proposed topology for positive half-cycle could be drawn as Fig. 8. Finally, the simplified single loop CM model of the proposed topology for positive half cycle is derived in Fig. 9. From Fig. 9, the following equation of the total CM voltage can easily be derived as:

$$V_{tCM} = V_{CM} + \frac{V_{DM}}{2} \frac{L_2 - L_1}{L_2 + L_1} \tag{5}$$

where VtCM represent total CM voltage, and L1 = L1A + L1g and L2 = L1B + L2g. In the proposed inverter if L1A = L1B and L1g = L2g for a well-designed circuit with symmetrically structured magnetics [16], equation (5) can be rewritten as follows:

$$V_{tCM} = V_{CM} = \frac{1}{2} (V_{1N} + V_{2N})$$

(6)

According to the operation principle of the proposed topology presented in section II (B), the total CM voltages can be calculated for each state of positive half cycle operation as follows:

$$\begin{aligned} \textit{State 1}: V_{tCM} &= \frac{1}{2} \left( V_{1N} + V_{2N} \right) = \frac{1}{2} \left( V_{PV} + 0 \right) = \frac{1}{2} V_{PV} \\ &\quad (7) \\ \textit{State 2}: V_{tCM} &= \frac{1}{2} \left( V_{1N} + V_{2N} \right) \\ &= \frac{1}{2} (1/2 V_{PV} + 1/2 V_{PV}) = \frac{1}{2} V_{PV} \\ \textit{State 3}: V_{tCM} &= \frac{1}{2} \left( V_{1N} + V_{2N} \right) = \frac{1}{2} \left( 0 + V_{PV} \right) = \frac{1}{2} V_{PV} \\ &\quad (9) \\ \textit{State 4}: V_{tCM} &= \frac{1}{2} \left( V_{1N} + V_{2N} \right) = \frac{1}{2} (1/2 V_{PV} + 1/2 V_{PV}) \\ &= \frac{1}{2} V_{PV} \end{aligned}$$

It is clear from equations (7)-(10) that the total CM voltage for the proposed topology during positive half cycle operation is kept constant at VPV/2.

Likewise, the total CM voltage for the negative half cycle operation can be calculated and found to be constant at VPV/2 due to the symmetry of operation for the positive and negative half cycle of grid current. The only difference is the activation of different power devices. Therefore, it can be concluded that the total CM voltage during the whole grid cycle is kept constant, reducing ground leakage current.

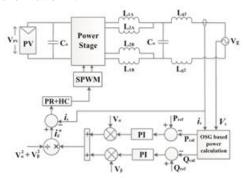

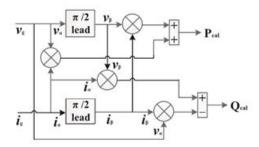

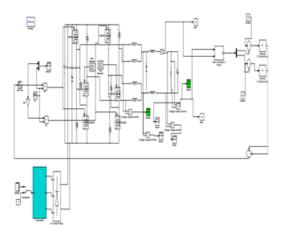

#### IV. PROPOSED TOPOLOGY CONTROL:

The control system for the proposed topology is illustrated in Fig. 10, which contains an orthogonal signal generator (OSG) unit to calculate active and reactive power, two proportional integral (PI) controllers, a grid current controller and a SPWM generation block. Based on the OSG system, the active power P and reactive power Q for the proposed topology can be calculated by using the following equation which is shown in Fig. 11 [4], [10]:

Pcal =1 /2[vgαigα + vgβigβ] (11) Qcal =1 /2[vgβigα –vgαigβ] (12) where vgα, vgβ, igα, and igβ represents the α and β components of grid voltage and current. Based on equation(11)and(12),the current in αβ-reference frame can be derived as follows: igα =2(Pcal \*vgα + Qcal \*vgβ)/\_v2gα + v2gβ\_ (13) igβ =2(Pcal \*vgβ + Qcal \*vgα)/\_v2gα + v2gβ\_ (14) According to the single phase P-Q theory, the grid-in current reference can be generated by regulating the averaged active and reactive power [5], [7]. Since the active and reactive power are constant in steady state, so to control them two PI.

Fig. 10. Control diagram of the proposed topology.

A Peer Reviewed Open Access International Journal

Fig. 11. OSG based power calculation.

Controllers has been used as shown in Fig. 10. The grid reference current can be derived with the help of OSG system in the following equation [5], [6]:

$$i_g^* = [(P_{ref} - P_{cal}) * G_p(s) * v_{g\alpha} + (Q_{ref} - Q_{cal}) * G_q(s) * v_{g\beta}]/$$

$$(v_{\alpha}^2 + v_{\beta}^2) \qquad (15)$$

where Pref and Qref are the power references, Gp(s) and Gq(s) are the transfer function of PI based controller that can be defined as follows:

$$G_p(s) = K_{pp} + K_{pi} * {}^1/_s$$

(16)

$$G_a(s) = K_{ap} + K_{ai} * \frac{1}{s}$$

(17)

where Kpp, Kpi, Kqp, and Kqi are the proportional and integral gain for the active and reactive power. In order to control the grid current, several existing control methods such as conventional PI controller, repetitive controller (RC), proportional resonant (PR) controller, and deadbeat (DB) controller can be adopted due to the capability of tracking reference signal without steady state error [27], [28]. Since the PR controller has better performance of tracking the reference signal if compared to the normal PI and RC controller, it is selected to control the output current of the proposed topology. The block diagram of the PR controller with harmonic current compensator is shown in Fig. 12, where Gc(s), Gh(s), and Gd(s) are the transfer function of fundamental current controller, harmonic compensator, and inverter respectively. The transfer functions are given below [7], [9]:

Fig. 12. Block diagram of PR controller with harmonic compensator.

## TABLE I SPECIFICATION OF THE PROTOTYPE:

| Inverter Parameter                                                                    | Value       |

|---------------------------------------------------------------------------------------|-------------|

| Input Voltage                                                                         | 400VDC      |

| Grid Voltage / Frequency                                                              | 230V / 50Hz |

| Switching Frequency                                                                   | 20kHz       |

| DC bus capacitor                                                                      | 470µF       |

| Filter capacitor                                                                      | 2.2µF       |

| Filter Inductor L <sub>1A</sub> , L <sub>2A</sub> , L <sub>1B</sub> , L <sub>2B</sub> | 1mH         |

| Filter Inductor Lg1, Lg2                                                              | 0.5mH       |

| PV parasitic capacitor Cpv1, Cpv2                                                     | 75nF        |

| MOSFET switches                                                                       | SPW47N60C3  |

| Diode (D1-D6)                                                                         | IDH08SG60C  |

| Controller                                                                            | dSPACE 1104 |

$$G_c(s) = K_{pi} + K_{ii} * \frac{s}{s^2 + \omega_f^2}$$

(18)

$$G_h(s) = \sum_{h=3,5,\dots} \frac{K_{ih}s}{s^2 + (h\omega_f)^2}$$

(19)

$$G_d(s) = \frac{1}{1 + 1.5T_s s} \tag{20}$$

Where Kpi andKii are the proportional and resonant gain,  $\omega f$  is the fundamental frequency, Kih is the resonant gain at the nth order harmonic, h is the harmonic order, and Ts is the sampling period.

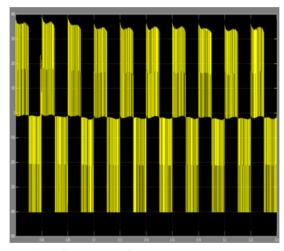

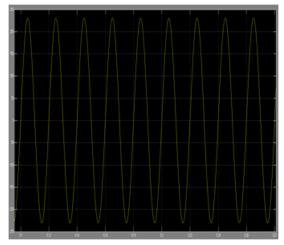

#### **V. SIMULATION RESULTS:**

The simulations are carried out MTALAB/Simulink software to analyze and initially verify the theoretical analysis. The parameters are used in simulation are given in Table I. The PV module is replaced with a 400V dc voltage source and the parasitic capacitance between the PV module and the ground is emulated using a thin film capacitor of 75nF. The simulated CM characteristics of the proposed topology with purereal power and both real and reactive power flow conditions are shown Figs. 13 and 14, respectively. It can be seen that the CM voltage((V1N +V2N)/2 for positive half cycle and (V3N +V4N)/2) for negative half cycle) for both unity power factor and other than unity power operation is

A Peer Reviewed Open Access International Journal

kept constant at the half of dc input voltage excluding a small fluctuation during the grid zero crossing instant. However, the ground leakage current is very small and its RMS value is only 10 mA which is far lower than the limitation requirement of the German standard [30]. Figs. 15 and 16 show the dynamic results under the changes of only Pref, and both Pref and Qref. It is clear that the grid current is changed according to the step load changes, and

Fig.13 Circuit diagram

Fig.14 Inverter 3-level output voltage

Fig.14 Load and grid voltage

The active and reactive power controller track the reference power within four cycle of operation. As seen, the grid current and voltage has very low distortion and the leakage flows through the whole system is very less. Therefore, it can be concluded that the fast and effective response of the load changes are achieved which validate the robustness of the proposed topology with the presented control scheme.

#### VII. CONCLUSION:

This paper explains a new high efficiency transformerless topology for grid-tied PV system is presented. The main advantages of the proposed topology can be summarized as:

- The inherent circuit configuration of the proposed topology does not lead itself to the reverse recovery issues which allow utilizing MOSFET switches even though when inject reactive power. Therefore, without compromising the overall efficiency, proposed topology can inject reactive power into the utility grid.

- The CM voltage is kept constant at the mid-point of dcbus voltage; as a result, low leakage current flows through the system which is lower than the H6-type topology.

PWM dead time is not required for the proposed to pology that reduces the THD at the output.

ISSN No: 2348-4845

## International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

Finally, to demonstrate the feasibility and effectiveness of the proposed topology, a 1 kW laboratory prototype is built and tested with both real and reactive power injection. The experimental results verified the above mentioned advantages. It has shown that the proposed topology presents almost the same characteristics for both real and reactive power injection, which are very suitable for grid-tied PV system. Therefore, it can be concluded that the proposed inverter is an attractive solution for grid-tied PV system.

#### **REFERENCES:**

- [1] I. Patrao, E. Figueres, F. González-Espín, and G. Garcerá, "Transformerless topologies for grid-connected single-phase photo-voltaic inverters," Renew. Sustain. Energy Rev., vol. 15, pp. 3423–3431, 2011.

- [2] M. Islam, S. Mekhilef, and M. Hasan, "Single phase transformerless inverter topologies for grid-tied photovoltaic system: A review," Renew. Sustain. Energy Rev., vol. 45, pp. 69–86, 2015.

- [3] I. PVPS, "Trends in photovoltaic applications. Survey report of selected IEA countries between 1992 and 2013," International Energy Agency, St. Ursen, Switzerland, Report IEA-PVPS T1–25, 2014.

- [4] Y. Yang and F. Blaabjerg, "Low-voltage ride-through capability of a single-stage single-phase photovoltaic system connected to the low-voltage grid," Int. J. Photoenergy, vol. 2013, pp. 1–9, 2013.

- [5] S. B. Kjaer, J. K. Pedersen, and F. Blaabjerg, "A review of single-phase grid-connected inverters for photovoltaic modules," IEEE Trans. Ind. Appl., vol. 41, no. 5, pp. 1292–1306, Sep./Oct. 2005.

- [6] X. Huafeng and X. Shaojun, "Leakage current analytical model and application in single-phase transformerless photovoltaic grid-connected inverter," IEEE Trans. Electromagn. Compat., vol. 52, no. 4, pp. 902–913, Nov. 2010.

- [7] T. Kerekes, R. Teodorescu, P. Rodriguez, G. Vazquez, and E. Aldabas, "A new high-efficiency single-phase transformerless PV inverter topol-ogy," IEEE Trans. Ind. Electron., vol. 58, no. 1, pp. 184–191, Jan. 2011.

- [8] Y. Bo, L. Wuhua, G. Yunjie, C. Wenfeng, and H. Xiangning, "Improved transformerless inverter with common-mode leakage current elimination for a photovoltaic grid-connected power system," IEEE Trans. Power Electron., vol. 27, no. 2, pp. 752–762, Feb. 2012.

- [9] M. Islam and S. Mekhilef, "H6-type transformerless single-phase inverter for grid-tied photovoltaic system," IET Power Electron., vol. 8, pp. 636–644, 2015.

- [10] O. Lopez et al., "Eliminating ground current in a transformerless pho-tovoltaic application," IEEE Trans. Energy Convers., vol. 25, no. 1, pp.140–147, Mar. 2010.

#### **Author's Details:**

#### **Ankuri Umarani**

Received B.Tech degree from medak college of Engineering & Technology, Kondapak, Siddipet, Telangana in 2015. And currently pursuing M.Tech in Power electronics at VIF college of Engineering & Technology, Moinabad, Ranga Reddy, Telangana.

**Tajvar Sultana**

Tajvar sultana obtained his BE (EEE) degree from Dr. VRK Women's College of Engineering in 2008, M.Tech (power electronics) from Royal Institute of Technology & Science in 2012.she has been working as a Associate Professor in dept. of EEE at VIF college of Engineering & Technology since 2013.