A Peer Reviewed Open Access International Journal

# A Implementation of Design Approach for Compressor Based Approximate Multipliers

Shaik Khasim Babu

Department of Electronics and Communication Engineering, Nimra College of Engineering Ibrahimpatnam, Vijayawada, A.P-521456, India.

### ABSTRACT:

Approximate computation can reduce the development sophistication by improving the efficiency and quality of error tolerant software. The summary addresses a new approach to multiplier estimation. To order to introduce various likelihood concepts, the component products of the multiplier are updated. The theoretical sophistication of estimation differs according to their probability to generate altered partial products. Two versions for 16-bit multipliers use the standard approximation. Synthesis findings show that two alternative multipliers produce 72% and 38% savings in energy, in contrast to an equivalent multiplier. respectively. These are more reliable than current estimated multipliers. For the suggested estimated multipliers, mean relative error values are as small as 7.6% and 0.02% which are higher than in previous works. The output of proposed multipliers is assessed by an algorithm to process the image, which generates the highest signal-to-noise ratio in one of the proposed models

Key words: Approximate computing, error analysis, low error, low power, multipliers.

### **INTRODUCTION**

In many electronic systems multipliers are one of the fundamental elements and, thus, are primarily concerned with the dissipation of their power and speed. Wherever the power utilization is the most critical factor, the skill dissipation should be minimized as much as possible for mobile applications [1]. The entire process of the adjustment, i.e. а full variety of signal transformations of the device, is one of the most effective ways of scales back from the complex power Md. Shamshad Department of Electronics and Communication Engineering, Nimra College of Engineering Ibrahimpatnam, Vijayawada, A.P-521456, India.

dissipation, which is now referred to as power dissipation in this article. Several attempts to study the dissipation of different multipliers are being committed.In the overly multiplier function, the major contribution to the total power usage is the output of a partial material. Tree multipliers, however, require massive storage in high-speed applications corresponding to filters. The base multipliers, based on the transmission select adder (CSA) [2], with a lower overhead storage, use a wide range of active transistors to replicate and thus use lots of power. Shift-and-add multipliers for its flexibility and comparatively small size requirements are used in many alternative applications.Nonetheless, higher-radix multipliers are quicker because they use larger recording, and because of their multiple sophisticated logic they require a great deal of storage for semiconductors. The multiplier function then measures the impact victimization, applies procedure and generates a stop signal alongside the 16bit output. This approach is implemented as an AN framework for a whole range of low-power high-order compressor architectures which fit 4-2 and 5-2 compressors which introduce fixed CMOS gates to victimize.For popular CMOS [3] cell engineering the resulting 2n + 1 multiplier function and squarer were improved and contrasted with the latest hardware implementations qualitarily and quantitatively. The study of the device gate design and therefore the experimental results show that the proposed installation

**Cite this article as:** Shaik Khasim Babu & Md. Shamshad, "A Implementation of Design Approach for Compressor Based Approximate Multipliers", International Journal & Magazine of Engineering, Technology, Management and Research, Volume 6 Issue 11, 2019, Page 25-30.

A Peer Reviewed Open Access International Journal

is quicker and uses less power compared to existing system implementations to maintain cost-effectiveness.

### **EXISTING SYSTEM**

Number implemented involves 3 steps: partial product creation, partial product decrease tree and finally, a vector merge extension to supply the final product by inserting and carriage of the decrease tree columns. Phase two requires extra energy. Approximation is used in the reduction tree stage during this temporary phase. For eg, an 8-bit unsigned1 number is used to illustrate the intended technique in multiplier approximation.The partial result at,n= $\alpha$ m=something close to the  $\beta$  in fig. 2 unmarked input operands at 80 m=  $\alpha$ m2m and  $\beta$  = 7n=0 $\beta$ n2n. First of all, the AND operating results are applied to the signed multiplication together with Booth multipliers, between the bits  $\alpha$ m and  $\beta$ n. The projected approximate technique shall also apply, except where no bits of signing extension are required [4].

| 1**   | 211             | 210                  | 2*             | 2"                      | 2'                       | 2*                                           | 1'                            | 2"                               | 2*                    | 21                  | 21             | 2              | 24             | 28           |

|-------|-----------------|----------------------|----------------|-------------------------|--------------------------|----------------------------------------------|-------------------------------|----------------------------------|-----------------------|---------------------|----------------|----------------|----------------|--------------|

| ē1,7  | $\bar{a}_{7,6}$ | $\bar{\alpha}_{7,2}$ | $\theta_{2,4}$ | $a_{2,3}$               | $\overline{a}_{7,2}$     | $\sigma_{7,1}$                               | $0_{10}$                      | 64.0                             | 41.0                  | $a_{i,i}$           | $\alpha_{3,0}$ | $\theta_{2,0}$ | $a_{1,0}$      | 61,0         |

|       | $\sigma_{6,7}$  | $6_{4,7}$            | $\theta G$     | $\theta_{3,7}$          | $\mathfrak{G}(t,\tau)$   | $\sigma_{r,\tau}$                            | $\theta_{0,7}$                | $\theta_{0,i}$                   | 44,1                  | $6_{0,4}$           | $\theta_{0,2}$ | $\theta_{0,2}$ | $q_{0,1}$      |              |

|       |                 | $a_{5,6}$            | 66,5           | $\phi_{6,d}$            | 46,2                     | $a_{6,2}$                                    | 66,7                          | $\theta_{i,l}$                   | 64.1                  | $a_{3,1}$           | $a_{2,2}$      | $a_{1,l}$      |                |              |

|       |                 |                      | $a_{5,6}$      | \$1,6                   | \$3,6                    | $\sigma_{2,6}$                               | $a_{i,i}$                     | 61,5                             | $a_{\ell,\ell}$       | $a_{i,1}$           | $a_{1,2}$      |                |                |              |

|       |                 |                      |                | 405.5                   | $a_{3,4}$                | $a_{5,2}$                                    | $\mathbf{n}_{5,2}$            | 44.2                             | $a_{1,2}$             | $a_{2,2}$           |                |                |                |              |

|       |                 |                      |                |                         | 44,5                     | $a_{3,5}$                                    | $\mathbf{n}_{2,2}$            | $\omega_{2,\ell}$                | $a_{2,3}$             |                     |                |                |                |              |

|       |                 |                      |                |                         |                          | $a_{\ell,\ell}$                              | $a_{i,i}$                     | $a_{2,3}$                        |                       |                     |                |                |                |              |

|       |                 |                      |                |                         |                          |                                              | $a_{3,\ell}$                  |                                  |                       |                     |                |                |                |              |

|       |                 |                      |                |                         |                          |                                              | I                             |                                  |                       |                     |                |                |                |              |

| 210   | 1 <sup>th</sup> | 14                   | 211            | 20                      | 2 <sup>1</sup>           | z <sup>a</sup>                               | ¥                             | zł                               | $\vec{x}^i$           | $\mathbf{z}^i$      | z <sup>k</sup> | zi             | 2 <sup>1</sup> | z            |

| 67.7  |                 |                      |                |                         |                          |                                              |                               |                                  |                       |                     |                |                |                |              |

| Ø7,7  | $0_{7,6}$       | $\theta_{C,1}$       | $p_{T,I}$      | $p_{2,3}$               | $\overline{P}^{2,2}$     | $p_{T,1}$                                    | $p_{2,3}$                     | $p_{i,s}$                        | $p_{1,0}$             | pur.                | pas.           | \$2,0          | $\sigma_{1,0}$ | 44,0         |

| 87,7  | 67,6<br>66,7    |                      |                |                         |                          |                                              |                               |                                  |                       | рия<br>Рэл          |                |                |                | 46,0         |

| Ø7,7  |                 |                      | ps.s           | $p_{i,i}$               | $p_{i,j}$                | <b>P</b> 6,2                                 | <b>p</b> <sub>62</sub>        | $p_{i,i}$                        | PLI                   |                     | p22            | 66,2           |                | 44,0         |

| Ø7,7  |                 | $a_{i,j}$            | ре.5<br>81,4   | рі, г<br>41, 5          | $p_{i,j}$                | рк;:<br>рі;;                                 | рю<br>рьз                     | рі,1<br>рі,2                     | P1.1<br>P1.2          | P2,1                | p2)<br>g20     | 66,2           |                | 94,0         |

| Ø7,7  |                 | $a_{i,j}$            | ре.5<br>81,4   | рі, г<br>41, 5          | Ры)<br>Ры<br>Пл          | рь;:<br>р5;1<br>64,4                         | рю<br>рьз                     | рі,1<br>р.с.<br>91,3             | P4.1<br>P3.2<br>\$5.8 | P3,1<br>62,2<br>g44 | p2)<br>g20     | 66,2           |                | #8,0         |

| Ø7,7  |                 | $a_{i,j}$            | ре.5<br>81,4   | рі, г<br>41, 5<br>Д', 2 | Ры)<br>Ры<br>Пл          | Р6,5<br>Р5,5<br>64,4<br>ВСЛ                  | ро<br>ро<br>ро                | ріл<br>ріл<br>яці<br>Віл         | PU<br>P2<br>部<br>部    | P3,1<br>62,2<br>g44 | p2)<br>g20     | 66,2           |                | #4,0         |

| Ø7,7  |                 | $a_{i,j}$            | ре.5<br>81,4   | рі, г<br>41, 5<br>Д', 2 | Р.)<br>Р.(<br>П.)<br>В.) | P6,2<br>P5,2<br>04,4<br>87,7<br>87,7<br>85,2 | ро)<br>раз<br>раз<br>да       | P(1<br>P(2<br>41,3<br>B(0<br>E(1 | PU<br>P2<br>部<br>部    | P3,1<br>62,2<br>g44 | p2)<br>g20     | 66,2           |                | #8,0         |

| \$7,7 |                 | $a_{i,j}$            | ре.5<br>81,4   | рі, г<br>41, 5<br>Д', 2 | Р.)<br>Р.(<br>П.)<br>В.) | P6,2<br>P5,2<br>04,4<br>87,7<br>87,7<br>85,2 | ро)<br>різ<br>роз<br>до<br>до | P(1<br>P(2<br>41,3<br>B(0<br>E(1 | PU<br>P2<br>部<br>部    | P3,1<br>62,2<br>g44 | p2)<br>g20     | 66,2           |                | <b>6</b> 4,0 |

Fig. 1. Transformation of generated partial products into altered partial products.

A partial item am, n gives one/4 probability of being 1 from the use of mathematics in learning. The partial product am, n and a, m square measure merged to create transmission and signal as shown in the columns with a substantial three partial products. The resulting signals scatter and produce partial material pm, n and gm, n as updated. In column three, the partial product am, n and a, m square calculate substituted by the modified partial products pm, n and gm, n, column eleven with the weight 211. Partial material matrices first and refurbished [5].

Pm,  $n = am, n + an, m gm, n = am, n \cdot an, m.$  (1)

The chance of the altered part-product g is 1/16, which is considerably less than 1/4 of am, n. There is a 1/16+3/16+3/16=7/16 probability that the partial output will be changed pm, which is above g, n. The parameters are rectangular, while approximation to the modified partial component matrix is added.

#### Approximation of Altered Partial Products gm,n

Column wise is done for building up the produced signals. Because every element is 1/16 probable to be one, two elements 1 also decreases in the same table. For example, in columns with four signals produced, all numbers are probably 0, (1 - pr) 4, only one is 4pr(1 - pr) 4pr)3, two elements are one in column, and 6pr2(1 - pr)2are one; three are 4pr3(1-pr) and all elements are 1 are pr4, with pr 1/16. The statistics for probabilities are provided for several m elements produced in each line. The OR gate create elements in the altered partial material matriz by means of the aggregation of the column In most instances, produces accurate results. Table also demonstrates the probability of error (Perr) through the use of OR gates to reduce the production of signal in each line [6]. The likelihood of confusion is very small, as can be seen. The likelihood of error decreases linearly as the amount of signals produced rises. But the failure rate always decreases. To prevent that, the maximum number of OR gate produced signals is 4. OR gates are used for a column with m signal production.

#### **Approximation of other Partial Products**

Approximate circuits are used to generate numerous partial items with probability 1/4 at midday, and 7/16 at evening. The square measure for its aggregation was approximately half adductor, total inserted mechanical system and 4-2 mechanical tool. Carry 2 inputs for those estimated loops and insert square measure. Since Carry has a higher binary bit weight, Carry bit errors can also add to the performance by having a 2 error distinction.Approximation is interpreted in a way that makes it absolutely essential to create a difference between actual output and estimated performance. Therefore, just provisional inputs for the instances,

A Peer Reviewed Open Access International Journal

wherever the contribution is approximated. XOR gates tend to add up and lag for adders and compressors. Of around half the gate of XOR attach, as given, this results in an error in the adding equation as shown in the true table in table II of the estimated half the gate. Ticks show the twin 2 estimated 4-2 is the product of non-zero performance even when all outputs are zero square. The output is not null in all situations. In particular in cases of zero bits entirely or in most of the important elements of the reduction tree, this leads to high disorder and high precision failure. This drawback is resolved by the proposed 4-2 mechanical device. For 4-2 mechanical devices, only 3-bit square calculation is required for the output if all four outputs are one out of seventeen instances. This method [7] is used to delete one function of the 3 mechanical unit output bits in 4-2. The output "100" (the value of 4) with four outputs being one must be replaced with output "11" (the value of 3) in order to take advantage of least error difference together. One of 3 XOR gates are substituted by a door to incorporate measurement. To order to make the add counterpart of the situation in which all the outputs are directly counted together, an optional circuit x1 to the add term is intercalar. For 5 out of 16 instances, it ends up for failure. The related table of facts is shown in Table II.

> $W1 = x1 \cdot x2$   $W2 = x3 \cdot x4$   $Sum = (x1 \bigoplus x2) + (x3 \bigoplus x4) + W1 \cdot W2$ Carry = W1 + W2.

It suggests an estimated eight in eight number decrease in the altered partial product matrix. It needs 2 phases to supply inserting and executing inputs for the application of vectors. 4 2-OR gates, 43-input OR gates and one square calculation of 4-input OO gates required to duck signal from 3 to eleven rows. The corresponding OR door steps are Gi identical to column I for weight 2i. The effect is Gi comparable. Three approximately halfthree estimated full-adders, and adders. three approximate square-measure compressors needed to supply add and y signals, Si and Ci equivalents to I are used for the reduction in specific partial material. The

mistreatment of roughly one half-adder and eleven total full-adders of the second stage sq. length manufacturing 2 final xi and Loloish operands to be supplied for rib carrying adder for the ultimate estimation of the product has been minimized. Two multiplier versions are supposed to weigh squarely. Approximation columns of n-bit-number partial component are used in the first example (Multiplier 1), while estimated circuits of square measure used in n - a least one of the columns of existence are used in Multiplier 2. The estimated square distance multipliers of n= seventeen. The square calculation multiplier is introduced in the compiler and TSMC type synthesized synopsy and Verilog Sixty-five nm galvanic cell library is contrasted with current theoretical multipliers at the regular system corner with a temperature of twenty-five ° C and voltage1 V. Inexact mechanical devices, a pair of ACM1, anywhere all columns are accepted, square and ACM2 wherever the only 15 less critical columns are approximated, are used to model mechanical devices based mainly on ACM1 multipliers. The SSM sort= 12 and n= 16 were planned for use. The palatopharyngoplanasty type of j=a pair of, k= a pair under the tree framework Dadda. The 16-bit partial product matrix below the specified number (UDM) contains approximately 2 tons of a pair of partial material obtained together with the current transport savings suppliers [8].

### **PROPOSED SYSTEM**

In order to further increase performance in order to reduce the error rate, the AN estimated mechanical model was developed. In most signal system algorithms, multiplication could be a simple procedure. There is huge capacity, lengthy latency and long power usage in multipliers. So the form of the low power number has a critical half in the VLSI process design of low power. The quality of the number mostly decides a process since the number is essentially the component and a great deal of roomOptimizing the number speed and storage is one of the most important issues in the design. Nevertheless, units of storage and velocity usually have inconsistent constraints, and speed changes correspond to larger areas. Multiplication could be a numerical

Volume No: 6 (2019), Issue No: 11 (November) www.ijmetmr.com

A Peer Reviewed Open Access International Journal

method that represents a certain number of times the task of applying AN variance to itself. Multiplicand distance is more often the time given to produce a result (product) by a different number (multiplier).Perform a significant part in the virtual process today and in numerous alternative applications. The influence of the expected multiplication compressors is explored throughout this section. Usually 3 components (or modules) consist of a strong (precise) number.

· Partial product generation.

• A carry save adder (CSA) tree to scale back the partial products' matrix to AN addition of solely 2 operands.

• A carry propagation adder (CPA) for the ultimate computation of the binary result.

The second module plays a key role in terms of the lag and the conceptual structure of power consumption gates in the form of a count. Compressors can therefore quickly and effectively boost the CSA tree and increasing its dissipation of energy. The use of estimated compressors corresponds to an approximate number of an AN in the CSA list. Signed without 8x8.

To assess the effect of victimization on the proposed compressors in estimated multipliers, the DADDA tree number is taken into consideration. The amount intended for this reason includes all partial products in the first quarter AND windows. The estimated compressors intended to scale back the partial products within the previous sectional unit in the CSA [9] tree in the second half. The last quarter is a qualified registered accountant with a certificate of qualification. This displays the digital reduction equipment of n 1/4 eight with a certain count. The quarter of the reduction utilizes partial chemicals, complete adds and 4-2 compressors; a dot is used for each portion of the material.In stage 1 2 halfadders, 2 full adders and a surface area of eight compressors were used to re-scale the partial products in a total of four columns. A half-adder, a whole-adder and ten compressor device will be attached to the 2 final lines of partial products during the second or third. Therefore, within the electronic reduction scheme of the 8x8 DDDA total, two decreasing stages and three 0.5

supplements, three full-adders ANd eighteen compressors area unit are required. Four instances field area group representative for AN estimated number preparation during this article.

• In the primary case (Multiplier 1), style one is employed for all 4-2 compressors.

• In the second case (Multiplier 2), style a pair of is employed for the 4-2 compressors. Since style a pair of doesn't have Cin and Cout, the reduction electronic equipment of this number needs a lower variety of compressors Number a pair of uses six half-adders, one full-adder and seventeen compressors. While the primary 2 planned multipliers have higher performance in terms of delay and power consumption, the error distances within the third and fourth styles area unit expected to be considerably lower. The DADDA number was designed by the mortal Luigi Dadda in 1965. it's just like Wallace number however slightly quicker and needs less gates. DADDA number was outlined in 3 steps:

• Multiply every little bit of} one argument with the every and each bit of alternative argument and continue till all arguments area unit increased.

• Reduce the quantity of partial merchandise to 2 layers of full and 0.5 adders. • Group the wires in 2 numbers, and add them with a traditional adder.

Approximate mechanical system development of AN is expected to further increase performance as the error rate is minimized. The expected equal amounts of estimated carry and cutting in the last quarter are often interchanged, as the inputs of carry and cut have a constant weight. During this new style, carry uses the right aspect of the side, and Cout always allows Cin good; as Cin is nil in the 1.In the theme, Cin and Cout are often overlooked. Image. Shows an estimated 4-2 mechanical system diagram and its outputs are also defined in the expressions below. This estimated design is to prolong the critical trip. This is not the case therefore with previous plans; however, there is a further decrease in the variety of windows.

Fig. 2 .Optimized 4-2 compressor

A Peer Reviewed Open Access International Journal

The approximate design for a 4-2 mechanical device, together with the exact decimal price for the input and, as such, the decimal price for the outputs produced by the approximate Compressor, is shown in this chart. The decimal value for incorporating outputs, e.g., once all the inputs weigh three, is four. The mechanical device, though, generates one for the whole train. In this case, the decimal value of the inputs is 3; the discrepancy is 1. This way, this design has 4 incorrect outputs out of 16 inputs, which actually decreases its error rate to 25 pc. This is often an outstanding feature, as it demonstrates that the imprecision of the intended model is, on a probabilistic level, less than the opposite of the schemes. Additives and compressors, XOR gates have a high volume and delay. The whole X-OR loop is substituted by the logic gate as shown with roughly the quarter adder. It corresponds to one mistake in the final estimate as shown in the estimated half-adder reality graph. A tick symbol indicates the correlation between incorrect performance and the right output and cross sign.

$$Sum = x1 + x2$$

Carr y = x1 • x2

One of the 2 XOR gates are substituted by logical gates in complete estimation in the approximation of maximum adder. In the last 2 instances, it corresponds to a failure out of 8. As in (3), Carr Y is altered when making a mistake. This simplifies a ton, while maintaining the difference between an initial and a loosely unified value. Approximate fullyadder table of facts is given

$$W = (x1 + x2)$$

$$Sum = W \bigoplus x3Carr y = W \cdot x3.$$

TRUTH TABLE OF APPROXIMATE FULL ADDER

|       | Inputs |    | Exa<br>Outp |     | Approx<br>Outp | Absolute |            |

|-------|--------|----|-------------|-----|----------------|----------|------------|

| $x_1$ | $x^2$  | x3 | Carry       | Sum | Carry          | Sum      | Difference |

| 0     | 0      | 0  | 0           | 0   | 0 🖌            | 0 🗸      | 0          |

| 0     | 0      | 1  | 0           | 1   | 0 🖌            | 1 🗸      | 0          |

| 0     | 1      | 0  | 0           | 1   | 0 🖌            | 11       | 0          |

| 0     | 1      | 1  | 1           | 0   | 11             | 0 🗸      | 0          |

| 1     | 0      | 0  | 0           | 1   | 0 🖌            | 11       | 0          |

| 1     | 0      | 1  | 1           | 0   | 1 🖌            | 0 🗸      | 0          |

| 1     | 1      | 0  | 1           | 0   | 0 X            | 1 X      | 1          |

| 1     | 1      | 1  | 1           | 1   | 1 🖌            | 0 X      | 1          |

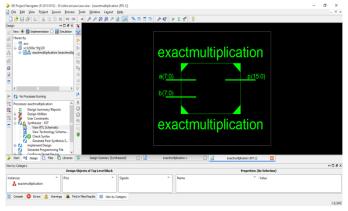

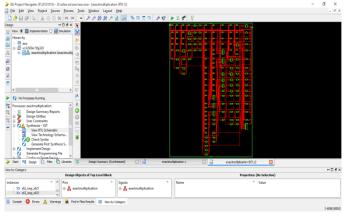

### SIMULATED RESULTS RTL

### INTERNAL BLOCK DIAGRAM

### AREA

| Device Utilization Summary                     |      |           |             |         |  |  |  |  |  |

|------------------------------------------------|------|-----------|-------------|---------|--|--|--|--|--|

| Logic Utilization                              | Used | Available | Utilization | Note(s) |  |  |  |  |  |

| Number of 4 input LUTs                         | 155  | 9,312     | 1%          |         |  |  |  |  |  |

| Number of occupied Slices                      | 87   | 4,656     | 1%          |         |  |  |  |  |  |

| Number of Slices containing only related logic | 87   | 87        | 100%        |         |  |  |  |  |  |

| Number of Slices containing unrelated logic    | 0    | 87        | 0%          |         |  |  |  |  |  |

| Total Number of 4 input LUTs                   | 155  | 9,312     | 1%          |         |  |  |  |  |  |

| Number of bonded <u>IOBs</u>                   | 32   | 232       | 13%         |         |  |  |  |  |  |

| Average Fanout of Non-Clock Nets               | 3.29 |           |             |         |  |  |  |  |  |

# DELAY

21.286ns (12.872ns logic, 8.414ns route) (60.5% logic, 39.5% route)

Total REAL time to Xst completion: 12.00 secs Total CPU time to Xst completion: 11.32 secs

A Peer Reviewed Open Access International Journal

### POWER

| B file Edit Year Isola Halp<br>D B   C O  ]                                                 |                                                                                                            |   |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---|

| Color Sensors                                                                               |                                                                                                            |   |

|                                                                                             | The Paren Andysis is up to date.                                                                           |   |

| Veve                                                                                        | Table View                                                                                                 |   |

| Design load 100% com<br>Running Vector-less<br>Finished Running Vec<br>Finished Running Vec | iite<br>Ghiristy Propagation<br>Co-laeg Activity Propagation 0 eess<br>Co-laeg Activity Propagation 0 eess |   |

|                                                                                             | ication.nod' and constraints 'exectmultiplication.pof' opened successfully                                 |   |

| Console Record Warrana                                                                      | fee .                                                                                                      | , |

| Deate Pages Harry                                                                           |                                                                                                            |   |

### SIMULATION RESULTS

#### CONCLUSION

DSP implementations are researched roughly for the digital image phase. Square estimation of literature articles of different estimated number strategies. Number implementing consists of three phases: partial product creation, partial product reduction tree, vector fusing addition to providing the final product from the minimum and holding tree lines. Step two requires extra energy.A completely unique mechanical tool based mainly on a rough number is expected to scale back energy and boost estimated separation. Approximate mechanical systems are further projected to increase efficiency as the error rate is increasing. Around 0.5 square tests adder and total adder and simulation performance. In combination with partial material and reduction phases, innovative mechanical devices are in part a pair in fashion.

#### REFERENCES

[1]. Chakradhar.S.T. and Raghunathan.A,(Jun 2010) "Best-effort computing:Re-thinking parallel software and hardware," in Proc. 47th ACM/IEEEDesignAutom. Conf., pp. 865–870. [2]. Gupta.V, Mohapatra.D, Park.S.P., Raghunathan.A, and Roy.K,(Aug 2011) "IMPACT: IMPreciseadders for low-power approximate computing," in Proc. Int. Symp. Low Power Electron Design, pp.409–414.

[3]. Jose.B and Radhakrishnan.D, (Dec 2006) "Delay optimized redundant binary adders," in Proc.13th IEEE Int. Conf. Electron., Circuits Syst. (ICECS), pp. 514–517.

[4]. Liang.J, Han.J, and Lombardi.F,(Sep 2013) "New metrics for the reliability of approximate and Probabilistic Adders" IEEE Trans Computers vol. 63, no. 9, pp. 1760–1771,

[5]. Liang.J, Han.J, and Lombardi.F,(Jun 2012) "New metrics for the reliability of approximate and probabilistic adders," IEEE Trans. Comput., vol. 62, no. 9, pp. 1760–1771,

[6]. Liu.C, Han.J, and Lombardi.F, (Mar. 2014) "A lowpower, high-performance approximate multiplier with configurable partial error recovery," in Proc.Conf. Design, Autom. Test Eur.,Art. no. 95.

[7]. Momeni.A, Han.J, Montuschi.P, and Lombardi.F,(Apr.2015) "Design and analysis of approximate compressors for multiplication," IEEE Trans.Comput., vol. 64, no. 4, pp. 984–994,

[8]. Ranger.C, Raghuraman.R, Penmetsa.A, Bradski.G, and Kozyrakis.C ,(Feb 2007) "Evaluating MapReduce for multi-core and multiprocessor systems," in Proc. IEEE 13th Int. Symp. High Perform. Comput. Archit. (HPCA),

[9]. Verma.A.K, Brisk.P, and Ienne.P,(Mar 2008) "Variable latency speculativeaddition: A new paradigm for arithmetic circuit design," in Proc. Design,Autom. Test Eur.,pp. 1250–1255.