# ISSN No: 2348-4845 International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

# Implementation Optimized Carry Select Adder Using Half Sum Half Carry Methodology

S.Khaja Hussain PG Scholar, Dept of ECE, Global College of Engineering & Technology, Kadapa, YSR (Dt), AP, India.

# **D.C.Vinod Kumar**

Assistant Professor, Dept of ECE, Global College of Engineering & Technology, Kadapa, YSR (Dt), AP, India.

To select the true sum and carry at each stage, a CMOS TG based 2:1 Mux is used.

# **II.RELATED WORK:**

Adder is most commonly used arithmetic block in applications like central processing unit (CPU) and digital signal processing (DSP) [1]. Therefore design of area efficient, low power and high performance adder circuit is of utmost importance [2] [3] [4] [5]. This paper presents the analysis of 16-bit addition operation using SQRT CSA and its performance is evaluated in terms of MOS transistor count, total power dissipation and propagation delay. The conventional SQRT CSA architecture uses multiple sets of ripple carry adder block at each stage to reduce area and power dissipation.

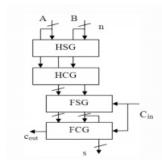

A modified SQRT CSA architecture is realized by replacing one ripple carry adder block with a binary-to-excess-1 converter [2] [3].All the building blocks of SQRT CSA are implemented with CMOS TG. Also, 1-bit full adder needed for CSA is designed using CMOS TG based XOR gates. In the modified SQRT CSA, the BEC block is implemented using standard cells of CMOS inverter, TG based XOR and AND gates. To select the true sum and carry at each stage, a CMOS TG based 2:1 Mux is used.

# III.IMPLEMENTATION LOGIC EXPRESSION OF BEC-BASED CSLA:

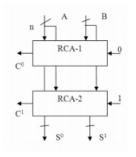

BEC-based CSLA consists of binary to excess-l converter in the place of RCA-2 in conventional CSLA as shown in Fig.4. The RCA is same as that of RAC-l in the conventional CSLA; it calculates n-bit sum {so I (i)} and

#### **ABSTRACT:**

The carry-ripple adder is composed of many cascaded single-bit full-adders. The circuit architecture is simple and area-efficient. However, the computation speed is slow because each full-adder can only start operation till the previous carry-out signal is ready. In the carry select adder, N bits adder is divided into M parts. Each part of adder is composed two carry ripple adders with cin\_0 and cin\_1, respectively. Through the multiplexer, we can select the correct output result according to the logic state of carry-in signal.

Area-efficient carry select adder by sharing the common Boolean logic term. After Boolean simplification, we can remove the duplicated adder cells in the conventional carry select adder. Alternatively, we generate duplicate carry-out and sum signal in each single bit adder cell. By utilizing the half sum and half carry implementation delay can be overcomes the parallel architecture in the conventional carry select adder.

#### Tags:

Carry Ripple Adder, Half Sum Half Carry, Binary To Excess Code.

# **I.INTRODUCTION:**

The conventional SQRT CSA architecture uses multiple sets of ripple carry adder block at each stage to reduce area and power dissipation. A modified SQRT CSA architecture is realized by replacing one ripple carry adder block with a binary-to-excess-1 converter. All the building blocks of SQRT CSA are implemented with CMOS TG. Also, 1-bit full adder needed for CSA is designed using CMOS TG based XOR gates . In the modified SQRT CSA, the BEC block is implemented using standard cells of CMOS inverter, TG based XOR and AND gates.

Volume No: 2 (2015), Issue No: 10 (October) www.ijmetmr.com

October 2015 Page 289

# ISSN No: 2348-4845 International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

carryout {CO out} corresponds to Cin = O. Inputs to the BEC unit is {so I (i), CO out} and output is (n+1)-bit excess-l code. The most significant bit (MSB) of the output of BEC unit represents Clout and remaining n least significant bits (LSBs) represents.

#### Fig.1. Structure of Ripple Carry Adder

Fig.2.Structure of SCG unit

The logic expressions of BEC-based CSLA is given as,

| $S_{1}^{1}(0) = s_{1}^{0}(0)$                             | (3a) |

|-----------------------------------------------------------|------|

| $C_{1}^{1}(0) = s_{1}^{0}(0)$                             | (3b) |

| $S_{1}^{1}(i) = s_{1}^{0}(i) \oplus c_{1}^{1}(i-1)$       | (3c) |

| $C_{1}^{1}(i) c = s_{1}^{0}(i).c_{1}^{1}(i-1)$            | (3d) |

| $C_{out}^{1} = c_{1}^{0} (n-1) \bigoplus c_{1}^{1} (n-1)$ | (3e) |

| (For $1 \le i \le n-1$ ).                                 |      |

From (3d) we can say that c I I depends on s o" in the case of conventional CSLA c I has no dependence on s\ Therefore BEC based CSLA has much data dependant compare to conventional CSLA. From (lc)-(2c) it can be observed that S O I and s I I are identical except the terms C O I and c I I since (so o=s I 0). In addition to that C O I and C 11 depend on {so, CO ,Cin}. Since C O I and c I have no data dependence on S O I and s I I the logic . ° I 'of c I and c I can be calculated before calculating and we can select any one from set using selection unit for the sum of CSLA. Most of the logic resources of CSLA are spent on calculating S1}d .Rejecting one sum-word is not efficient approach after calculation of two sums. Instead of this we can select any one of carry words using carry input Cin for calculating final sum.

# IV.RESULTS: RCA Carry Select Adder

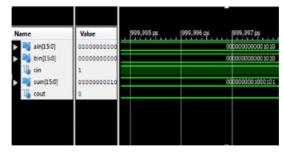

Fig 3: RCA carry select adder resultant

Ripple carry select adder is a mux based implementation as discussed in the chapter2.The resultant is show in the above result with carry given 1.

### **Proposed Adder:**

| Name         | Value    | 1999,995 ps | 999,996 ps | 999,997 pt |

|--------------|----------|-------------|------------|------------|

| 🕨 👔 sum(7:0) | 00001111 |             |            | 0000111    |

| lý dk        | 0        |             |            |            |

| lig on       | 1        |             |            |            |

| ar 10        | 00001001 |             |            | 0000100    |

| ► Tá b[7:0]  | 00000101 |             |            | 0000010    |

|              |          |             |            |            |

|              |          |             |            |            |

|              |          |             |            |            |

#### Fig 4: proposed adder simulation result

Proposed adder is implemented using half sum and half carry method .To input a and b are 9 and 5 respectively .and the carry is 1.the final resultant is 15 shown in sum with 8 bits

|            | proposed | conventional |

|------------|----------|--------------|

| slices     | 25       | 25           |

| Flip flops | 43       | 46           |

| 4 input    | 42       | 43           |

| luts       |          |              |

| Iob        | 26       | 50           |

Volume No: 2 (2015), Issue No: 10 (October) www.ijmetmr.com

# ISSN No: 2348-4845 International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

### **V.CONCLUSION:**

After Boolean simplification, we can remove the duplicated adder cells in the conventional carry select adder. Alternatively, we generate duplicate carry-out and sum signal in each single bit adder cell. By utilizing the half sum and half carry implementation delay can be overcomes the parallel architecture in the conventional carry select adder. In this way, the circuit area and lut count can be greatly reduced and power delay product of the adder circuit can be also greatly lowered

### **REFERENCES:**

[1] Binary adder architecture for cell based VLSI and their synthesis by "RETO ZIMMERMANN"

[2] Bedrij O. J, "Carry-select adder", IRE Transaction on Electronic Computers, pp.340–344, 1962.

[3] Brent R. P and Kung H. T., "A Regular Layout for Parallel Adders", IEEE Transaction on computers, Vol. C-31, No.3, p.260-264, March, 1982.

[4] Ceiang T. Y and Hsiao M. J, "Carry-select adder using single ripplecarry adder", Electronics Letters, vol. 34, no. 22, pp. 2101–2103,October 1998.

[5] Kim Y and L-S Kim, "bit carry-select adder with reduced area", Electronics Letters, vol. 37, pp. 614-615, May 2001.

### **Author's Profile:**

S Khaja Hussain, Pursuing M.Tech (VLSI), Global College of Engineering & Technology, Kadapa, Andhra Pradesh, India.

D.C.Vinod Kumar, M.Tech, Assistant Professor at Global College of Engineering & Technology, Kadapa, Andhra Pradesh, India.