A Peer Reviewed Open Access International Journal

# **Transformer less Single-Phase Inverter with Hybrid Modulation**

N.Vidyarani M.Tech Student, Department of EPID, Sindhura College of Engineering & Technology.

B.Ravi Kiran Assistant Professor, Department of EEE, Sindhura College of Engineering & Technology.

U.Krishna Prasad Associate Professor, Department of EEE, Sindhura College of Engineering & Technology.

#### Abstract:

This paper gives high-proficiency single-stage transformer less inverter with hybrid modulation method is proposed and assessed. Without input split capacitors, common-mode voltage and leakage current issues in a non-isolated framework with this design are disposed of, and the peculiarity of a three-level output voltage in the inverter bridge's middle point helps inductors and power quality enhancement. The operation standards with hybrid modulation strategy combined with unipolar and bipolar pulse width modulation schemes are displayed.

#### **Index Terms:**

Common-mode voltage, hybrid modulation method, leakage current.

### I. INTRODUCTION:

In recent years, grid-connected systems have become more and more widespread in private and commercial applications. Non-isolated inverters with decreased number of components, low cost, and high efficiency are preferred choices for these applications, where power density, cost, weight, and reliability are critical issues. However, these inverters suffer from some safety and power quality drawbacks, such as commonmode voltage or ground leakage current issue between grid and dc current injection into the grid. The traditional full-bridge inverter with four active switches is simple and has a good tradeoff between efficiency, complexity, and price. Its efficiency can reach 97% with unipolar pulse width modulation method. However, it generates a commonmode voltage with an amplitude of half input voltage at the switching frequency, which needs a big CM choke. This problem could be eliminated by the same topology with bipolar PWM scheme, but the efficiency is limited to 95.3% and requires a bigger output differential filter than that with unipolar modulation strategy. The parasitic capacitor between the PV array and the ground also plays an important role in a CM voltage or ground leakage current issue. The CM voltage across the capacitor generates a ground leakage current, which may cause severe electromagnetic interference (EMI) problem, grid current distortion, and additional losses in the system, etc.

Figure 1: Some novel inverters without ground leakage issues. (a) H5 circuit from SMA Corporation. (b) HERIC topology from Sunways Company. (c) HB-ZVR circuitry from Aalborg University.

A Peer Reviewed Open Access International Journal

## II.COMMON-MODE VOLTAGE AND LEAKAGE CURRENT ANALYSIS:

Without galvanic isolation between the grid and the PV system, the galvanic connection between them results in the appearances of a CM resonant circuit consisting of stray capacitance Cpv, representing the PV module to the ground and the filters, as illustrated in Fig. 2, where ZGcGg is the series impedance between the ground connection points of the inverter and the grid [8]. Fig. 3(a) further shows its corresponding CM noise detail model. Without EMI filter and ZGcGg considered, the simplified model, as shown in Fig. 3(b), is given by (1), i.e.,

Figure 2: Leakage current in H4 topology

$$v_{\rm cm\_total} = v_{\rm cm} + v_{\rm dm} \cdot \frac{L_2 - L_1}{2(L_2 + L_1)}$$

In order to simplify the analysis, inductances of L1 and L2 are assumed the same; thus, th e CM noise from a DM noise source in Fig. (3) and (1) is ignored here. For the CM voltage hot points locate d at inverter bridge middle points A and B, the instanta neous CM voltage and ground leakage current could be given by the following equation:

$$v_{\rm cm\_total} = v_{\rm cm} = \frac{v_{AN} + v_{BN}}{2}$$

(2)

$$i_{\rm cm} = C_{\rm pv} \frac{dv_{\rm cm}}{dt}$$

(3)

where vAN and vBN are the pulse voltage s between the branch midpoint and the dc bus min us terminal, respectively. It is easy to conclude that, if

$$v_{\rm cm} = \frac{v_{AN} + v_{BN}}{2} = \text{const}_{(4)}$$

The possible CM voltage and leakage current are avoided. Otherwise, large CM chokes have to be added to the output terminals that have high impedances at high frequency to suppress C M noise. It requires the CM inductors to be quite big, h eavy, and expensive.

### A. H4 Topology With Bipolar Modulation:

With the bipolar modulation scheme u sed in H4 topology, the diagonal switch pairs S1, S 4 and S2, S3 are switched alternatively. When S1, S4 are on,

$$v_{AN} = V_{dc}, \quad v_{BN} = 0 \Rightarrow v_{cm} = \frac{v_{AN} + v_{BN}}{2} = \frac{V_{dc}}{2}$$

(5)

When S2, S3 are on,

$$v_{AN} = 0$$

,  $v_{BN} = V_{dc} \Rightarrow v_{cm} = \frac{v_{AN} + v_{BN}}{2} = \frac{V_{dc}}{2}$  (6)

### **B.** H4 Topology With Unipolar Modulation:

Unlike that with bipolar modulation, the H4 topology with unipolar modulation has two active switches, i.e., S2 and S4 that are only tu rned on/off in line with frequency. In addition, th e other two switches, i.e., S1 and S3, are high-frequenc y switches. Thus, switching losses are decreased, and VAN and VBN are threelevel voltages, which can improve the current ripple in the output inductors. Taking the positive grid halfcycle as an example, S4 i s always on, and S1 switches at switching frequency fs. When S1, S4 are on, the CM voltage is given by

$$v_{AN} = V_{dc}, \quad v_{BN} = 0 \Rightarrow v_{cm} = \frac{v_{AN} + v_{BN}}{2} = \frac{V_{dc}}{2}$$

(7)

When S1 is turned off and S4 is still on, the body diode of S3 naturally provides a freewheeling path, i.e.,

$$v_{AN} = 0, \quad v_{BN} = 0 \Rightarrow v_{cm} = \frac{v_{AN} + v_{BN}}{2} = 0$$

(8)

It is observed that the CM voltage cha nges between Vdc/2 and 0 at switching frequency fs , which will produce a large CM current in the stray cap acitance Cpv.

A Peer Reviewed Open Access International Journal

### **C.Proposed H6 Inverter and Modulation Strategy**

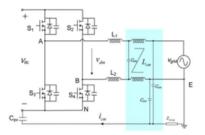

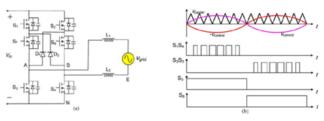

### Figure 3: Proposed H6 topology with hybr id modulation method. (a) H6 topology. (b) Hybrid modulation method.

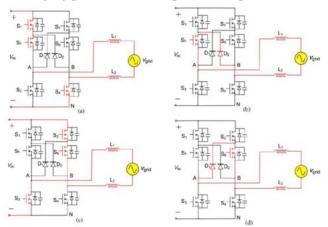

**Mode 1:** In the grid positive half-cycle, S5 is always on, where S1, S4 are active. The input voltage applied to the inductors L1 and L2 is the difference b etween the input and grid voltages; thus, the current is charging. In this mode, the CM voltage is given by

$$v_{AN} = V_{dc}, \quad v_{BN} = 0 \Rightarrow v_{cm} = \frac{v_{AN} + v_{BN}}{2} = \frac{V_{dc}}{2}$$

(10)

**Mode 2:** In the grid positive half-cycle, S5 is still on, where S1, S4 are inactive. In addition, D2 co mmutates at the PWM switching frequency. It provide s a freewheeling path to maintain an inductor current, which is discharging by the grid voltage. At this ti me, the input voltage is shared between parasitic capacitors of switches S1 and S3 because the large impe dance of inactive switches blocks the discharging pro cess of these parasitic capacitors.

Figure 4: Operation modes . (a) Mode 1. (b) Mode 2. (c) Mode 3. (d) Mode 4.

$v_{AN} \approx \frac{V_{

m dc}}{2}, v_{BN} \approx \frac{V_{

m dc}}{2} \Rightarrow v_{

m cm} = \frac{v_{AN} + v_{BN}}{2} \approx \frac{V_{

m dc}}{2}$  (11)

Modes 3 and 4: similarly change during the grid negative half-cycle, where vdm changes between 0 and -Vdc/2 Under the conditions that Modes 1-4 illustrated, CM voltage vcm keeps an almost constant value of half input voltage Vdc/2. It means that the inverter with hybrid modulation method has a high performance in CM noise elimination. In addition, because parasitic capacitors of switches are used instead of input split capacitors, there is no need to establish a split dc link, to that pulse voltages between two bridge midpoints and dc bus minus terminals are complementary three-level voltages. Their sum is 2vcm, which remains almost constant at the value of the input voltage, except some high frequency noise, particularly at the zero-crossing zone of the grid voltage.

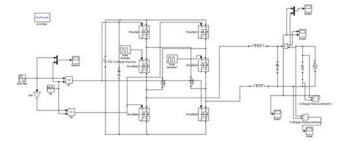

#### (a) Matlab Simulation Circuit

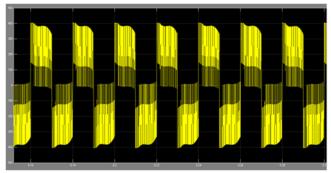

(b) Inverter output voltage

A Peer Reviewed Open Access International Journal

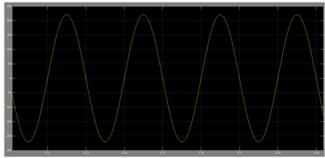

## (c) Grid voltage

**Figure 5: Simulation results.**

### **III. CONCLUSION:**

Derivation rules of high-efficiency inverters without leakage current issue have been summarized in this paper, where unidirectional freewheeling cells are embedded in the middle point of the bipolar inverter. Based on this concept, inverter topology derivation and standardizing is possible. In addition, the topology is also proved to be a variation of the inverter. Following the variation rules, a novel high-efficiency single-phase transformer less inverter with hybrid modulation method has been proposed and validated as an example in this paper. Common-mode voltage and leakage current issues in a non-isolated system with H6-type configuration are eliminated without input split capacitors. In addition, steady-state characteristics, loss analysis, simulation, and experimental results are provided to show excellent DM and high-efficiency features of the inverter.

#### **REFERENCES:**

- J. Myrzik and M. Calais, "String and module integrated inverters for single-phase grid connected photovoltaic system–A review," in Proc. IEEE Bologna Power Tech Conf., Bologna, Italy, Jun. 2003, pp. 1–7.

- [2] J. M. Carrasco, L. G. Franquelo, J. T. Bialasiewicz, E. Galvan, R. C. P. Guisado, Ma. A. M. Prats, J. I. Leon, and N. Moreno-Alfonso, "Power-electronic systems for the grid integration of renewable energy sources: A survey," IEEE Trans. Ind. Electron., vol. 53, no. 4, pp. 1002–1016, Jun. 2008.

- [3] O. Lopez, R. Teosorescu, F. Freijedo, and J. DovalGandoy, "Leakage current evaluation of a single phase transformerless PV inverter connected to the grid," in Proc. IEEE Appl. Power Electron. Conf., Anaheim, CA, Feb 2007, pp. 907–912.

- [4] M. Armstrong, D. J. Atkinson, C. M. Johnson, and T. D. Abeyasekera, "Auto-calibrating DC link current sensing technique for transformerless, grid connected, H-bridge inverter systems," IEEE Trans. Power Electron., vol. 21, no. 5, pp. 1385– 1393, Sep. 2006.

- [5] D. Holmes and T. Lipo, Pulse Width Modulation for Power Converters: Principles and Practice. New York: Wiley, 2003.

- [6] R. Gonzalez, J. Lopez, P. Sanchis, E. Gubia, A. Ursua, and L. Marroyo, "High-efficiency transformerless single-phase photovoltaic inverter," in Proc. IEEE EPE-PEMC, Aug./Sep. 2006, pp. 1895–1900.

- [7] DKE, DIN V VDE V 0126-1-1, Automatic Disconnection Device Between a Generator and the Public Low-Voltage Grid. Berlin, Germany: VDE Press, 2006.

- [8] R. Gonzalez, E. Gubia, J. Lopez, and L. Marroyo, "Transformerless single-phase multilevel-based photovoltaic inverter," IEEE Trans. Ind.Electron., vol. 55, no. 7, pp. 2694–2702, Jul. 2008.

- [9] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," IEEE Trans. Ind. Appl., vol. IA-17, no. 5, pp. 518– 523,Sep. 1981.

- [10] M. C. Cavalcanti, A. M. Farias, K. C. de Oliveira, F. A. S. Neves, and J. L. Afonso, "Eliminating leakage currents in neutral point clamped inverters for photovoltaic systems," IEEE Trans. Ind. Electron., vol. 59, no. 1, pp. 435–443, Jan 2012.

A Peer Reviewed Open Access International Journal

- [11] S. Aeaujo, P. Zacharias, and R. Mallwitz, "Highly efficient single-phase transformerless inverters for grid-connected photovoltaic systems," IEEE Trans. Ind. Electron., vol. 57, no. 9, pp. 3118–3128, Sep. 2010.

- [12] H. Schmidtr, C. Siedle, and J. Ketterer, "DC/AC converter to convert direct electric voltage into alternating voltage or into alternating current," U.S. Patent Application, Publication Number US7046534 B2, May 2006.

- [13] M. Victor, F. Greizer, S. Bremicker, and U. Hubler, "Method of converting a direct current voltage from a source of direct current voltage, more specifically from a photovoltaic course of direct current voltage, into a alternating current voltage," U.S. Patent Application, Publication Number US2005/0286281 A1, Dec. 29, 2005.

- [14] T. Kerekes, G. Vazquez, R. Teodorescu, P. Rodriguez, and E. Aldabas, "A new highefficiency single-phase transformerless PV inverter topology," IEEE Trans. Ind. Electron., vol. 58, no. 1, pp. 184–191, Jan. 2011.

- [15] X. Zhang, L. Sun, P. Xu, W. Zhao, and R. Cao, "Research on commonmode current reduction of nonisolated single-phase gridconnected photovoltaic systems," Acta Energiae Sol. Sin., vol. 30, no. 9, pp. 1203–1207, Sep. 2009.

- [16] W. Yu, J.-S. Lai, H. Quian, and C. Hutchens, "High-efficiency MOSFET inverter with H6-type configuration for photovoltaic nonisolated ACmodule applications," IEEE Trans. Power Electron., vol. 26,no. 4, pp. 1253–1260, Apr. 2011.

- [17] M. C. Cavalcanti, K. C. de Oliveira, A. M. de Farias, F. A. S. Neves, G. M. S. Azevedo, and F. C. Camboim, "Modulation techniques to eliminate leakage currents in transformerless three-phase photovoltaic systems," IEEE Trans. Ind. Electron.,

vol. 57, no. 4, pp. 1360-1368, Apr. 2010.

- [18] F. Bradaschia, M. C. Cavalcanti, P. E. P. Ferraz, F. A. S. Neves, E. C. dos Santos, and J. H. G. M. da Silva, "Modulation for three-phase transformerless Z-source inverter to reduce leakage currents in photovoltaic systems," IEEE Trans. Ind. Electron., vol. 58, no. 12, pp. 5385– 5395, Dec. 2011.

- [19] T. Nguyen and H. H. Lee, "Modulation strategies to reduce commonmode voltage for indirect matrix converters," IEEE Trans. Ind. Electron., vol. 59, no. 1, pp. 129–140, Jan 2012.

- [20] Y. Jang and M. M. Jovanovic, "A bridgeless PFC boost rectifier with optimized magnetic utilization," IEEE Trans. Power Electron., vol. 24, no. 1, pp. 85–93, Jan. 2009.

- [21] H. Qian, J.-S. Lai, and W. Yu, "Novel bidirectional ac-dc MOSFET converter for energy storage system applications," in Proc. IEEE Energy Convers. Congr. Expo., Phoenix, AZ, Sep. 2011, pp. 3466–3471.

- [22] S. Clemente, "A simple tool for the selection of IGBTs for motor drives and UPSs," in Proc. IEEE Appl. Power Electron. Conf., Dallas, TX, Mar. 1995, pp. 755–764.

- [23] J.-S. Lai, R. W. Young, G. W. Ott, Jr, and J. W. McKeever, "Efficiency modeling and evaluation of a resonant snubber based softswitching inverter or motor drive applications," in Proc. IEEE Power Electron. Spec. Conf., Atlanta, GA, Jun. 1995, pp. 943–949.

- [24] D. Graovac, M. Purschel, and A. Kiep, "MOSFET power losses calculation using the data-sheet parameters," Infineon Technol., Dresden, Germany, Jul. 2006, Appl. note.

A Peer Reviewed Open Access International Journal

[25] R.-Y. Kim, J.-S. Lai, B. York, and A. Koran, "Analysis and design of maximum power point tracking scheme for thermoelectric battery energy storage system," IEEE Trans. Ind. Electron., vol. 56, no. 9, pp. 3709–3716, Sep. 2009.

### **Author's Details**

**N.Vidyarani,** Received B.Tech degree from Sindhura college of engineering & technology, Medipaly, Godavarikhani (N.T.P.C) Ramagundam, Dist. Karimnagar, Telangana in 2014. And currently pursuing M.Tech in Electrical power industrial drives at from Sindhura college of engineering & technology, Medipaly, Godavarikhani (N.T.P.C) Ramagundam, Dist. Karimnagar, Telangana.

**B.Ravi Kiran,** Obtained My B.Tech (EEE) degree from BHARATH INSTITUTE OF ENGINEERING AND TECHNOLOGY in 2009, M.Tech. (Power engineering and enery systems) from SREE CHAITANYA INSTITUTE OF TECHNOLOGICAL SCIENCES in 2014. I am working as Asst. Prof. in SINDHURA COLLEGE OF ENGINEERING AND TECHNOLOGICAL since 2014. My interest area includes powersystems and electrical machines. And I Have 2 years teaching experience.

**U.Krishna Prasad,** Obtained My B.Tech (EEE) degree from SR Engineering College in 2008, M.Tech. (Power Electronics) from Vaagdevi college of Engineering in 2011. I worked as Asst. Prof. in SREE CHAITANYA INSTITUTE OF TECHNOLOGICAL SCIENCES. And I am working as an Associate Professor in dept. of EEE at Sindhura College of engineering and technological since 2014. My interest area includes power electronics and electrical machines. And I Have 5 years teaching experience.