A Peer Reviewed Open Access International Journal

# Design and Analysis of Combinational Circuit for Efficient Fault Coverages Using Built-In Self Test

# V.Ashok Kumar

Head of the Department,

Department of ECE

Patnam Rajender Reddy Memorial Engineering

College,

Shabad.

### Abstract

A new fault coverage test pattern generator using a linear feedback shift register (LFSR) called FC-LFSR can perform fault analysis and reduce the power of a circuit during test by generating three intermediate patterns between the random patterns by reducing the hardware utilization. The goal of having intermediate patterns is to reduce the transitional activities of Primary Inputs (PI) which eventually reduces the switching activities inside the Circuit under Test (CUT) and hence power consumption is also reduced without any penalty in the hardware resources.

Keywords- LFSR, Optimization, Low Power, Test Pattern Generation, BIST

# INTRODUCTION Objective:

The VLSI circuit manufacturer cannot guarantee the defect free integrated circuits(IC's). This makes us to evolve a fast accurate means of testing such circuits. In a small-scale environment, it may not be feasible to invest large sums of money into complex IC testers. In labs till now we are having Digital testers which will test IC's based on some non functional parameters like temperature, any short circuits in the IC etc. & are used for testing only Combinational circuits. In this paper, the validation is based on functionality of IC. The digital pattern generator and logic analyzer are used to test the combinational, sequential circuits.

This paper describes a versatile but inexpensive, testing system for standard digital IC's (7400-series

**Shrama Parveen**

M.Tech Student

Department of ECE

Patnam Rajender Reddy Memorial Engineering

College,

Shabad.

transistor-transistor logic (TTL)[1] based on the use of a FPGA. This tester can be economically implemented for small or medium-scale users of such IC's & provides a quick but thorough checkout of most small & medium-scale functions with minimal operator action. Dedicated special-purpose hardware is minimal, allowing this tester to be implemented on virtually FPGA.

Each IC is tested by applying test patterns to input pins of the chip & the resulting chip outputs are then examined for errors resulting from the stuck-at conditions or other functional errors [3]. For Dedicated ATE, all input & output patterns expected outputs, For Generalized ATE, the DUT output can be stored in the Logic analyzer & user need to check the functionality based on the input & output results. This ATE can be used to test the combinational and sequential circuits. The test set for each IC is an exhaustive set of all possible input combinations; this ATE is used for SSI & MSI functions.

# **Introduction to Automated Test Equipment:**

The automated test equipment is useful for functional testing, debug of new designs and failure analysis of existing designs. The automated test equipment can be used early in the design cycle to substitute for system components that are not yet available. For example, a automated test equipment might be programmed to send interrupts and data to a newly developed bus circuit when the processor that would normally provide the signals doesn't yet exist. automated test equipment consists of

1. Frequency synthesizer

A Peer Reviewed Open Access International Journal

- 2. Switch matrix

- 3. Control blocks

# **Thesis Motivation:**

Automatic or Automated Test Equipment (ATE) is any apparatus that performs tests on a device, known as the Device Under Test (DUT) or Unit Under Test (UUT), using automation to quickly perform measurements and evaluate the test results. ATE systems are designed to reduce the amount of test time needed to verify that a particular operation. One ATE tests several (usually identical) devices at the same time. DUT has greater than 1 circuit. ATE handles multiple devices simultaneously.

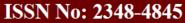

# **BASIC BIST ARCHITECTURE**

The various components of BIST hardware are the test pattern generator (TPG), the test controller, circuit under test (CUT), input isolation circuitry and the output response analyzer (ORA). This is shown in the figure 2.1 below.

Fig 2.1 Basic BIST architecture.

# **Test Pattern Generator (TPG):**

Responsible for generating the test vectors according to the desired technique (i.e. depending upon the desired fault coverage and the specific faults to be tested for) for the CUT. Linear feedback shift register (LFSR) and pseudo random pattern generator (PRPG) are the most widely used TPGs.

### **Test Controller:**

Responsible for controlling the other components to perform the self test. The test controller places the CUT in test mode and allows the TPG to drive the circuit's inputs directly. During the test sequence, the controller interacts with the ORA to ensure that the proper signals are being compared. The test controller asserts its single output signal to indicate that testing has completed, and that the ORA has determined whether the circuit is faulty or fault-free.

# **Output Response Analyzer (ORA):**

Responsible for validating the output responses i.e. the response of the system to the applied test vectors needs to be analyzed. Also, a decision is made about the system being faulty or fault-free. LFSR and multiple input signature register (MISR) are the

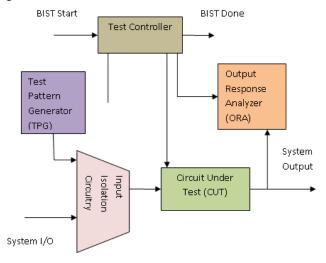

# **DESIGN OF ATE**

The digital pattern generator is useful for functional testing, debug of new designs and failure analysis of existing designs. The digital pattern generator can be used early in the design cycle to substitute for system components that are not yet available. For example, a digital pattern generator might be programmed to send interrupts and data to a newly developed bus circuit when the processor that would normally provide the signals doesn't yet exist. Digital Pattern Generator (DPG) consists of

- 1. Frequency synthesizer

- 2. Switch matrix

- 3. Control blocks

Fig.3.1. Block diagram of Automatic Test Equipment for Digital Integrated Circuits

A Peer Reviewed Open Access International Journal

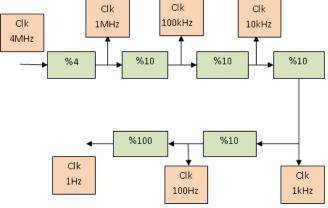

# Frequency synthesizer:

Frequency synthesizer will produce frequency signals by the excitation of a 4MHz clock signal. The clock signal has been generated from a crystal oscillator which generates six different frequencies ranging from 1 Hz to 1 MHz Frequency Synthesizer is nothing but designing different counters so that required clock frequency can be obtained. Sparten2 FPGA consists of 4 MHz crystal oscillator. As shown in the figure 3.2, six different frequencies are generated first by using mod 4 counter 1 MHz clock. . Use 1Mhz as a clock and give it to mod 10 counter to generate 100Khz in the same way three more mod 10 counters are used to obtain 10Khz,1Khz and 100hz.finally to generate 1hz mod 100 counter is used by giving 100hz as a clock.

Fig.3.2.Generation of different frequency signals

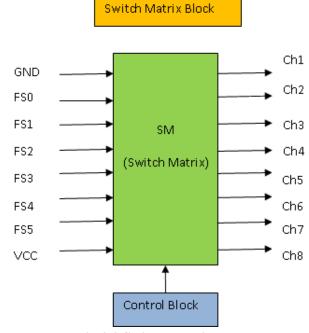

# **Switch Matrix:**

A switch matrix is used in test systems, in both design verification and manufacturing test, to route high frequency signals between the device under test (DUT) and measurement equipment. Since the signal routing and signal conditioning needs for a test system differ from design to design, Switch Matrices typically have to be custom designed by the test system engineer for each new test system. The variable frequencies from FSB output along with logic 1 and logic 0 are feed to switch matrix as shown in figure 3. The command from the control logic block to switch matrix is based on the DUT. Logic 1's and logic 0's are selected for the combinational circuits and different frequency signals are selected for sequential circuits. So the test

hardware is essentially independent of the test chip. Changing from one logic family to another can be made by simply changing the command from the command register.

Fig.3.3.Switch Matrix Block

The internal switch configuration of switch matrix as explained in figure 3.3, consists of eight 8:1 multiplexers. Each multiplexer has six inputs from frequency synthesis block and other two are Vcc and ground. The select line signals for each multiplexer was generated from control block based on DUT. If the DUT is any basic gate then select lines will be generated by basic gates control block. If the DUT is combinational integrated circuit then select lines will be generated by generalized combinational control block. The select lines will be generated by generalized sequential control block if the DUT is sequential integrated circuit.

# **DUT:**

# **XOR** gate:

The XOR gate (sometimes EOR gate, or EXOR gate and pronounced as Exclusive OR gate) is a digital logic gate that implements an exclusive or; that is, a true output (1/HIGH) results if one, and only one, of the inputs to the gate is true. If both inputs are false

A Peer Reviewed Open Access International Journal

(0/LOW) and both are true, a false output results. XOR represents the inequality function, i.e., the output is true if the inputs are not alike otherwise the output is false. A way to remember XOR is "one or the other but not both".

Fig.3.4.XOR gate

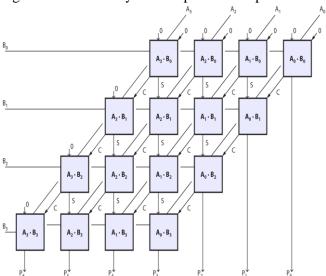

The parallel multiplier circuit operates on 8-bit unsigned operands and produces a 16-bit unsigned product. The parallel multiplier consists of three logic blocks: the partial product generators, the partial product reduction logic, and a final parallel adder. Figure 44 details the organization of the partial product generation and reduction logic. The final parallel adder is equivalent to the parallel adder circuit used in the add functional unit. The organization of the final parallel adder is shown in Figure 3.5. Each partial product is formed through the logical ANDing of a multiplier bit and a multiplicand bit. Eight rows of eight partial product generators are shown in Figure 4.3. Booth recoding of the partial products is not employed in this multiplier. The partial product reduction logic transforms the array of partial product bits into a redundant binary form of the product. The redundant binary form of the product is converted to the simple binary result by the final parallel adder. The partial product reduction logic consists of two levels of (4,2) counters. In the first level, one set of eleven counters com- presses from one to four bits of partial product in each of the eleven columns of binary precedence formed by the multiplication multiplicand by the least significant four bits of the multiplier while another set of eleven counters reduce the partial product bits formed by the multiplication of the multiplicand by the most significant four bits of the multiplier.

The implementation of multipliers is considered first. Xilinx FPGAs such as Spartan-II as well as Virtex devices and Altera FPGAs such as APEX and Cyclone

II devices have fast carry logic and dedicated AND gate for each of the Look Up Tables (LUTs) in the Slices/Logic Elements (LEs). Since multiplying an N bit number by 2 requires only AND gates and adders, fast Nx2 multipliers can be implemented using this dedicated hardware [10 & 11]. To implement a Nx4 multiplier, output of two Nx2 multipliers has to be added [12]. To implement an NxM multiplier, the output of rlog2M7, Nx2 multipliers have to be added, 2 at a time in parallel in rlog2M7 stages appropriately.

The dotted line indicates points where registers may be inserted for pipelining. For wave-pipelining all the stages are directly connected without registers. The registers are used only at the inputs and outputs.

Fig.3.5.Multiplication of two numbers

# **Control Block:**

This module consists of three control blocks namely basic gates control block, generalized combinational control block, generalized sequential control block. The control blocks will generates the twenty four bit pattern which is used as select input signals to all the eight multiplexers, three bits to each multiplexer. The command register will receives the input signals from FPGA switches and enables the control block accordingly. Each control block generates the different select line signals based on DUT.

A Peer Reviewed Open Access International Journal

# **XOR** gate control block:

The input conditions of xor gate are generated by using this control gate module. The below values are the test conditions

| A | В |

|---|---|

| 0 | 0 |

| 0 | 1 |

| 1 | 0 |

| 1 | 1 |

# **Combination control block:**

The input conditions of multiplier are generated by using this control gate module. The bellow values are the test conditions

| A    | В    |

|------|------|

| 0000 | 0000 |

|      | 0001 |

|      | 0010 |

|      |      |

|      | 1111 |

| 0001 | 0000 |

|      | 0001 |

|      | 0010 |

|      |      |

|      | 1111 |

| 1111 | 0000 |

|      | 0001 |

|      | 0010 |

|      |      |

|      | 1111 |

# **Memory Control Block:**

In this memory control block, write and read signals are activated. Address and Data values are generated depends upon the write and read conditions.

# Logic Analyzer:

A logic analyzer is an electronic instrument which displays signals of a digital circuit and used to check and analyze the test outputs. A logic analyzer may convert the captured data into timing diagrams, protocol decodes, state machine traces, assembly language, or correlate assembly with source-level software.

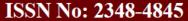

# Flow chart

A Peer Reviewed Open Access International Journal

By using the command register and switch matrix the logic blocks, combinational blocks, sequential block are given as input to the DUT and then to the logic analyzer. Logic analyzer consists of the saved logic, combinational and sequential blocks where the DUT three blocks are tested for the fault by comparing with the logic analyzer. If the given blocks are fault free the output is given as correct if there is any fault the output is again given to the DUT

# **RESULTS & DISCUSSION**

The power consumed by the chip under test is a measure of the switching activity of the logic inside the chip which depends largely on the randomness of the applied input stimulus. The existing technologies reduced correlation between the successive vectors of the applied stimulus into the CUT can result in much higher power consumption by the device. The increased power may be responsible for cost, reliability, performance verification, autonomy and technology related problems.

# **Synthesis Report:**

Minimum period: 4.007ns (Maximum Frequency: 249.563MHz)

Minimum input arrival time before clock: 8.424ns Maximum output required time after clock: 17.999ns Maximum combinational path delay: 20.608ns.

# **RTL Schematic:**

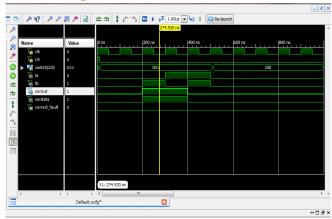

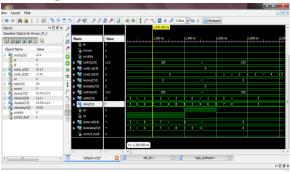

# Simulation: Logic Control:

# **Correct Output**

# **Fault output**

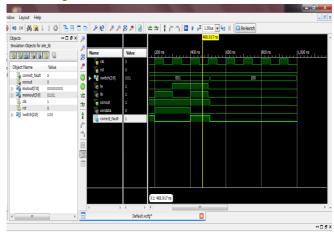

# **Array Multiplier:**

# **Correct output**

A Peer Reviewed Open Access International Journal

# **Fault output**

# **Memory:**

# **Correct output**

# **Fault output**

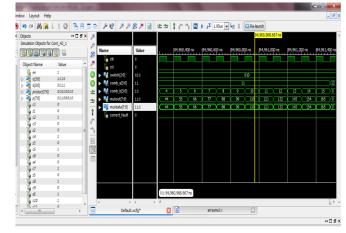

# **Overall output:**

# **Correct output**

# **CONCLUSION**

The paper proposed an optimization procedure for Test Pattern Generation (TPG) technique with reducing power dissipation during testing along with fault coverage. The transition is reduced by increasing the correlation between the successive bits, reduces the power of a circuit during the test mode. By increasing the correlation between the test patterns in the CUT and eventually the power consumption is reduced. The circuit is tested during the presence of fault and without fault for fault coverage .so, compared toe to existing the proposed method got less delay so that it we can say the proposed method is efficient in fault coverages.

# REFERENCES

- [1] Afzali.A, Alisaface.M, Atoofian.E, Hatami.S and Navabi.Z,,,,,A New Low-Power Scan-Path Architecture, "" IEEE International Symposium, Vol.5, pp.5278 5281, 23-26 May 2005.

- [2] Crouch.A,,,,,Design-for-Test for Digital IC's and Embedded Core Systems," Prentice Hall, 1999.

- [3] Polian, A. Czutro, S. Kundu, and B. Becker, "Power droop testing," in Proceedings of the 24th International Conference on Computer Design (ICCD '06), pp. 243–250, October 2006.

- [4] H. Fai and N. Nicolici, "Automated scan chain division for reducing shift and capture power during broadside at-speed test," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 27, no. 11, pp. 2092–2097, 2008.

- [5] S. J. Wang, K. L. Fu, and K. S. M. Li, "Low peak power ATPG for n-detection test," in Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS '09), pp. 1993–1996, May 2009.

- [6] P. Girard, "Survey of low-power testing of VLSI circuits," IEEE Design and Test of Computers, vol. 19, no. 3, pp. 80–90, 2002.

ISSN No: 2348-4845

# International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

- [7] M. ElShoukry, C. P. Ravikumar, and M. Tehranipoor, "Partial gating optimization for power reduction during test application," in Proceedings of the 14th Asian Test Symposium (ATS '05), pp. 242–245, ind, December 2005.

- [8] Y. Zorian, "A Distributed BIST Control Scheme for Complex VLSI Devices," in Proc. VLSI Test Symp. (VTS"93), pp. 4-9, 1993.

- [9] S. Wang and S. Gupta, "DS-LFSR: A New BIST TPG for Low Heat Dissipation," in Proc. Int. Test Conf. (ITC"97), pp. 848-857, 1997.

- [10] F. Corno, M. Rebaudengo, M. Reorda, G. Squillero and M. Violante, "Low Power BIST via Non-Linear Hybrid Cellular Automata," in Proc.VLSI Test Symp. (VTS"00), pp. 29-34, 2000.

- [11] Girard et al.P, "A Modified Clock Scheme for a Low Power BIST Test Pattern Generator," Proc. 19th VLSI Test Symp. (VTS 01), IEEE CS Press, Los Alamitos, Calif., 2001, pp. 306-311.

- [12] S. Wang and S. Gupta, "LT-RTPG: A New Test-Per-Scan BIST TPG for Low Heat Dissipation," in Proc. Int. Test Conf. (ITC"99), pp. 85-94, 1999.

- [13] S. Wang, "Generation of Low Power Dissipation and High Fault Coverage Patterns for Scan-Based BIST," in Proc. Int. Test Conf. (ITC"02), pp. 834-843, 2002.

- [14] N. Basturkmen, S. Reddy and I. Pomeranz, "A Low power Pseudo-Random BIST Technique," in Proc. Int. Conf. on Computer Design (ICCD"02), pp. 468-473, 2002.

- [15] Roy.K and Zhang.X, "Peak Power Reduction in Low Power BIST," in Proc. Int. Symp. on Quality Elect. Design (ISQED"01), pp. 425-432, 2001.

- [16] Mehrdad Nourani, Mohammad Tehranipoor, Nisar Ahmed,,,,,Low- Transition LFSR for BIST-

Based Applications,""14th Asian Test Symposium, pp. 138-143, 18-21 Dec. 2005. 176

# **Author Details**

# V.Ashok Kumar Head of the Department, Department of ECE Patnam Rajender Reddy Memorial Engineering College, Shabad.

### Shrama Parveen

M.Tech Student

Department of ECE

Patnam Rajender Reddy Memorial Engineering

College,

Shabad.