A Peer Reviewed Open Access International Journal

# Energy and Area Efficient Three-Input XOR/XNORs with Systematic Cell Design Methodology

N.Indu Priya M.Tech,

Dr.K.V.Subba Reddy Institute of Technology.

#### **Abstract:**

An efficient three-input XOR/XNOR circuits as the most significant blocks of digital systems with a new systematic cell design methodology (SCDM) in hybrid-CMOS logic style is proposed in this project. SCDM, which is an extension of CDM, plays the essential role in designing efficient circuits. At first, it is deliberately given priority to general design goals in a base structure of circuits. This structure is generated systematically by employing binary decision diagram. After that, concerning high flexibility in design targets, SCDM aims to specific ones in the remaining three steps, which are wise selections of basic cells and amend mechanisms, as well as transistor sizing. In the end, the resultant three-input XOR/XNORs enjoy fullswing and fairly balanced outputs.we can extend this project for designing of full adder design and it's topologies.

#### **Index Terms:**

Binary decision diagram applications, energy efficiency, hybrid-CMOS logic style, systematic design methodology, three-input XOR/XNOR circuits.

## **I.INTRODUCTION:**

The exclusive-OR (XOR) and exclusive-NOR (XNOR) gates are the essential parts of several digital systems and are highly used in very large scale integration (VLSI) systems such as parity checkers, comparators, crypto processors, arithmetic and logic circuits, test pattern generators, especially in Full adder module as Sum output that is 3-input XOR and so forth. In most of these systems, XOR and XNOR gates constitute a part of the critical path of the system, which significantly affects the worst-case delay and the overall performance of the system.

R.Prabhakar, M.Tech, (Ph.D)

Associate Professor,

Dr.K.V.Subba Reddy Institute of Technology.

ISSN No: 2348-4845

An optimized design is desired to avoid any degradation on the output voltage, consume less power, and have less delay in critical path with low-supply voltage as we scale toward deep sub-micron technology. Other desired features for the design are to have a small number of transistors to implement the circuit. In particular, for XOR and XNOR circuits, the simultaneous generation of the two-nonskewed outputs is highly desirable. As known, the switching speed of the balanced XOR and XNOR functions, comparing with those designs that use an inverter to generate the complement signal, is increased by eliminating the inverter from the critical path. Thus the design methodology for 3-input XOR/XNOR circuits is introduced.

## II.CELL DESIGN METHODOLOGY FOR LOW-POWER HIGH-SPEED BALANCED THREE-INPUT XORXNOR IN HYBRID-CMOS LOGIC STYLE

## 2.1The Introduction of Basic Cells

This methodology is based on using different basic cells and optimization mechanisms. To obtain basic cells, 3-input XOR/XNOR function is investigated. For choosing the mechanisms, we use the simulation results of in which the balanced two inputs XOR/XNOR circuits based on the Cell2 have possessed better results.

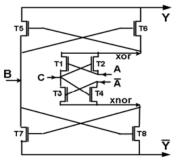

### A. Basic Cell: Version I:

We present the first version of the elementary basic cell (referred to as BC1) in "Fig. 1". In this cell, all six transistors are nMOS. Truth table of the BC1 in "Fig. 1" shows the output levels of this circuit for each input vector. To convert BC1 to an XOR–XNOR circuit that produces full swing output signals, it is necessary to

A Peer Reviewed Open Access International Journal

replace high impedance outputs with logic "1" or "0". Moreover, in order to obtain better performance, non full-swing outputs for some input vectors must be converted into full swing signals.

| В | A | C | XOR3 | XNOR3 |

|---|---|---|------|-------|

| 0 | 0 | 0 | Hi-z | Hi-z  |

| 0 | 0 | 1 | Hi-z | 0     |

| 0 | 1 | 0 | Hi-z | Hi-z  |

| 0 | 1 | 1 | 0    | Hi-z  |

| 1 | 0 | 0 | Hi-z | 0     |

| 1 | 0 | 1 | 0    | 1-    |

| 1 | 1 | 0 | 0    | Hi-z  |

| 1 | 1 | 1 | 1-   | 0     |

Fig 1: BC1 circuit and input and output values

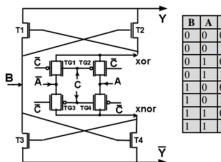

### **B. Basic Cell: Version II:**

We present basic cell 2 (referred as BC2) in Fig. 2.3. In this cell, nMOS transistors for all four external section boxes and transition gate for central section boxes are selected. Fig. 2 shows outputs for each input vector. In order to convert the BC2 into an XOR–XNOR circuit, which provides full swing operation, it is necessary that the high impedance states of outputs in Fig. 2 be replaced with "1". We also have to optimize the circuit using various methods to eliminate the non full-swing operation.

| В | A | C | XOR3 | XNOR3 |

|---|---|---|------|-------|

| 0 | 0 | 0 | 0    | Hi-z  |

| 0 | 0 | 1 | Hi-z | 0     |

| 0 | 1 | 0 | Hi-z | 0     |

| 0 | 1 | 1 | 0    | Hi-z  |

| 1 | 0 | 0 | 1-   | 0     |

| 1 | 0 | 1 | 0    | 1-    |

| 1 | 1 | 0 | 0    | 1-    |

| 1 | 1 | 1 | 1-   | 0     |

Fig 2: BC2 circuit and input and output values.

## C. Correction and optimization mechanisms:

Correction and optimization mechanisms are pull up/down networks, feedback networks, bootstrap technique, output inverters and combinational mechanism named after applying the two mechanisms simultaneously on basic cell.

## 2.2 INTRODUCTION OF BALANCED 3-INPUT XOR-XNOR CIRCUITS

To convert these cells into balanced 3-input XOR-XNOR circuits with acceptable performance, two main steps should be employed. In the first step, the high impedance output states should be eliminated. In the second step, non full-swing output signals should be fixed. Three selected mechanisms such as feedback networks and combinational mechanisms such as pull up/down with feedback networks and pull up/down networks with bootstrap technique are applied and presented the circuits with names XO1 through XO6 in Table I.

# TABLE I. INTRODUCTION OF XOR/XNOR CIRCUITS IN DIFFERENT CLASSES WITH THEIR MECHANISMS

| Class | Name | Basic<br>cell | Feedback<br>network | Pull up/down<br>network | Bootstrap<br>technique |

|-------|------|---------------|---------------------|-------------------------|------------------------|

| A     | XO1  | BC1           | Fc                  |                         | -                      |

| A     | XO2  | BC2           | Fp                  | -                       | -                      |

| n     | XO3  | BC1           | Fc                  | <b>√</b>                | -                      |

| В     | XO4  | BC2           | Fp                  | <b>√</b>                | -                      |

| C     | XO5  | BC1           | -                   | <b>V</b>                | n                      |

| C     | XO6  | BC2           | -                   | <b>√</b>                | р                      |

## A. Class A 3-input XOR-XNOR Circuits

A circuits are introduced (Table I). This group of circuits uses feedback network mechanisms to convert the basic cells into XOR-XNOR circuits providing full swing output signals. For each one of the basic cells, we select a proper feedback network. We present Class A circuits with the names XO1 and XO2 in Fig. 3.

Fig 3: New 3-input XOR/XNOR Circuits- XO1 and XO2.

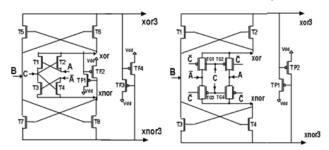

#### **B. Class B 3-input XOR-XNOR Circuits**

Class B circuits are a group of XOR-XNOR circuits (Table I) in which pull up and pull down networks and

A Peer Reviewed Open Access International Journal

feedback networks are used simultaneously. In this class pull up and pull down networks are used to eliminate critical states and feedback networks are employed to rectify the output levels. Class B circuits, XO3 and XO4, are presented in Fig. 4.

Fig 4: New 3-input XOR/XNOR Circuits- XO3 and XO4.

## C. Class C 3-input XOR-XNOR Circuits

Class C circuits include XOR–XNOR circuits in which bootstrap technique has been used to ensure the full swing operation, and the high impedance states at the outputs have been corrected using pull up and pull down networks. This technique could be used for BC1 and BC2 since they all suffer from the no full voltage swing as well as the high impedance states at the output nodes. Circuits XO5 and XO6 in class C are optimized versions of BC1 and BC2 respectively. Class C circuits that are introduced in Table I and Fig.5 employ the combinational mechanisms.

Fig 5: New 3-input XOR/XNOR Circuits- XO5 and XO6

## III.SCDM FOR THREE-INPUT XOR/XNOR CIRCUITS

#### 3.1 INTRODUCTION

With the rapid growth of portable electronic devices, it is becoming a critical challenge to design low-power, high-speed (LPHS) circuits that occupy small chip areas. We see many published papers that compete in designing better circuits. Such studies mostly rely on creative design ideas but do not follow a systematic approach. As a consequence, most of them suffer from some different disadvantages.

- 1) They are implemented with logic styles that have an incomplete voltage swing in some internal nodes, which leads to static power dissipation.

- Most of them suffer from severe output signal degradation and cannot sustain low-voltage operation.

- 3) They predominantly have dynamic power consumption for non-balanced propagation delay inside and outside circuits, which results in glitches at the outputs. Therefore, a well-organized design methodology can be regarded as a strong solution for the challenge. Cell design methodology (CDM) has been presented to design some limited functions, such as two-input XOR/XNOR and carry—inverse carry in the hybrid-CMOS style.In the second stage, CDM is matured as systematic CDM (SCDM) in designing the three-input XOR/XNORs for the first time.

#### **3.2 SCDM:**

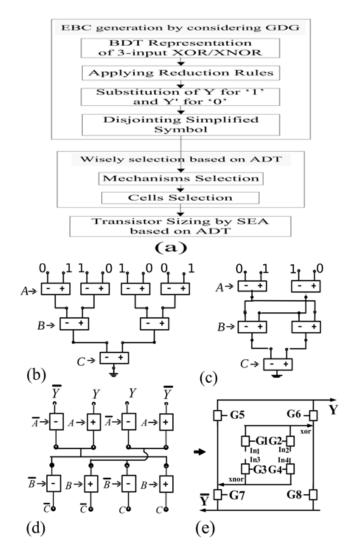

In this section, the methodology for three-input XOR/XNORs is presented according to the flowchart. The design path is started by EBC systematic generation. In this step, general design goals are considered that the most distinctive ones generating fairly balanced outputs, symmetric and power-ground-free structure, fewer transistors in the critical path, as well as sharing common sub circuit. Systematic generation process of . In the remaining steps, the methodology offers opportunity to strive toward an assigned design target. Two of these steps include wisely selection of mechanisms and basic cells from PDP point of view. An in-depth analysis for the selection Fig. in terms of PDP. In the last step, in order to put the resultant circuits in proper state, a sizing algorithm consistent with the methodology is indispensable.

A Peer Reviewed Open Access International Journal

Fig. 6: (a) SCDM process for designing efficient three-input XOR/XNORs. (b) BDT representation of three-input XOR/XNOR function. (c) Applying reduction rules. (d) Substitution and disjointing. (e) EBC.

## 3.3 Elementary Basic Cell Systematic Generation

In order to generate the EBC of three-input XOR/XNOR circuits, four steps are taken. The process has been shown in Fig. 6(b)–(e). Initially, three-input XOR and its complement is represented by one binary decision tree (BDT) in order to share common sub circuits. The BDT is achieved by some cascaded  $2 \times 1$  MUX blocks, which are denoted by simplified symbol controlled with input variables at each correspondent

level. This construction simply implements the minterms of the three-input XOR/XNOR function, as shown in Fig. 6(b). The step is followed by applying reduction rules to simplify the BDT representation. These include elimination, merging, and coupling rules. The major task of the coupling rule, in simple terms, is to obtain all the possible equivalent trees by interchanging the order of the controls. The trees are acquired by impacting the state matrix on the corresponding control matrix where the multiply and add operators operate as follows:

$$\begin{array}{ccc}

0^{\cdot} \chi_{i} &= \overline{\chi} \\

1^{\cdot} \chi_{i} &= \chi \\

\chi_{1} + \chi_{2} + \cdots + \chi_{m} &= \chi_{1} \chi_{2} \dots \chi_{m} &= 11 \dots 1 &= I_{2^{m}-1}.

\end{array}$$

The result of applying the reduction rules to the tree is shown in Fig. 6(c). Afterward, as the inputs into the first level are 0's and 1's of the function's truth table, the 0 and 1 can be replaced by the Y and Y, respectively. Finally, the simplified symbol can be divided into two distinct symbols: 1) the plus sign with the x input control and 2) the minus sign with the x input control. The result of applying steps 3 and 4 is shown in Fig. 6(d). The EBC, which is extracted from the above procedure, has been presented in Fig. 6(e). This cell has eight elements, deciding two outputs. We refer to the pins of the central section (IN1–IN4 and G1–G4) as A or C, or their complements. We also assume that pins of the external section G5–G8 can also be B or its complement.

### 3.4 Wisely Selection of Mechanisms and Cells

By replacing the elements with pass transistors or transmission gates and the control inputs with input signals in combination with optimization and correction mechanisms, a huge circuit library is achieved as each circuit can be appropriate for specific applications. The selection is meditated to determine dominant mechanisms and cells, in terms of PDP, power, and delay when the optimization goal is PDP. The results are used to produce circuits for high-performance portable electronic applications. Mechanisms include optimization mechanisms to resolve nonfull swing [inverter (I) and feedback (F)],

A Peer Reviewed Open Access International Journal

correction mechanisms to resolve high impedance [pull up-down network (P) and feedback (F)], or the combinations of them [bootstrap-pull (BP) up-down, feedback pull (FP) up-down, bootstrap-feedback (BF), inverter-feedback (IF), and inverter-pull (IP) up-down]. Mechanisms are divided into three categories: 1) cells with both nMOS and pMOS in EBC structure (C1);

- 2) onlynMOS (C2); and

- 3) onlypMOS (C3).

To reduce complexity, we have also considered the central part of EBC and to achieve real results, the circuits have been simulated in the chain test bench. The circuits have been named with the abbreviation of the mechanism (or cell) being utilized, while the other circumstances, cells, or mechanisms are assumed to be fixed. Using transmission gates in EBC, which is called TG, the complete circuit is achieved as there is no need for any other mechanisms. Therefore, TG is compared separately with others. The first experiment that studies the performance of the inverter mechanism shows I suffers from more power and PDP in comparison with other mechanisms. The increase in the static power consumption and switching delay of I are due to nonfull swing drive of the inverter. However, BP brings advantages in power reduction using blocking voltage in intermediate nodes to shift the gate voltage.

The next experiment extends to investigate transistors' area of the mechanisms rather than the basic cells when the difference in circuits is their utilized mechanisms. We roughly estimated the transistors' area by adding the area ( $W \times L$ ) of all the transistors that is i Wi Li. Although the number of mechanism transistors in some cases is more than the basic cell transistors, BCTA occupies the most area in the majority of circuits. This is because the mechanism transistors are responsible for gate driving, such as in B, or resolving high impedance of only some states, such as in F and P, which are weaker responsibilities compared with that of the cell transistors for output generation.

Therefore, the sizing algorithm also tends to choose the mechanism transistors' area to be smaller than BCTA.In the next experiment, we address feedback mechanism. The F network, when the cell is meditating to change the outputs, tries to keep the previous state, which gives rise to a struggle. This initial struggle causes the voltage step, as well as delay and power to increase. Therefore, the sizing algorithm chooses small sizes for F transistors not to be dominated. The struggle will be more critical when the F transistors are driven by the nonfull swing outputs or they should resolve solely the high impedance problem, because they should be strong enough to do the duty. The stronger the F transistors, the more the struggle and their consequences are more likely to happen. As a result, in these cases, it is better that high impedance duty is solved by P. The last experiment investigates the basic cells to characterize the cell, which outperforms in all mechanisms. According to the figure, C2 with the most numbers of nMOS transistors in its structure enjoys better results. The worst one is C3 with the largest number of pMOSs.

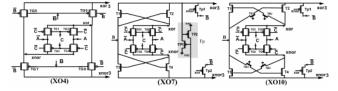

Taken all the above points together, under the assumptions about the technology and the domain of circuits, the individual mechanism, I, does not present proper performance in terms of power and delay. This is while I was introduced as the only solution for nonfull swing outputs in many papers. Due to the high power consumption, I in combinational mechanism, such as IF and IP, operate worse than both BF and BP. The high impedance problem is also better resolved by P as we can observe IP to IF and BP to BF perform superior. Next, using transmission gate in EBC and TG enjoys the least power, delay, and PDP as a complete part that does not need any mechanisms. In the end, the individual mechanism, F, with suitable transistor sizing is capable of playing a key role besides the dominant combinational mechanisms, BP and FP, for the wisely design when PDP is target.Based on the findings, circuits with names XO1 through XO10 are presented, whose the building structure details with the average PDP are tabulated in Table II.

A Peer Reviewed Open Access International Journal

# TABLE II: INTRODUCTION OF THE STRUCTURE OF THREE-INPUT XOR/XNOR CIRCUITS WITH THE AVERAGE PDP IN FEMTOJOULE

| centeral part |            |     |   | external part |            |     |          |          |      |

|---------------|------------|-----|---|---------------|------------|-----|----------|----------|------|

| Circuits      | mechanisms |     |   |               | mechanisms |     |          | avg      |      |

|               | BC         | F   | В | P             | BC         | F   | В        | P        | PDP  |

| XO1           | TG         |     |   |               | C1         | Fnp | -        | -        | 1.27 |

| XO2           | C2         | Fnp | - | -             | C2         | Fnp | -        | -        | 0.70 |

| XO3           | TG         |     |   |               | C2         | Fp  | -        | -        | 0.62 |

| XO4           | TG         |     |   |               |            | TG  |          |          |      |

| XO5           | TG         |     |   | C1            | Fnp        | -   | <b>√</b> | 0.71     |      |

| XO6           | C2         | Fnp | - | -             | C2         | Fnp | -        | <b>√</b> | 0.57 |

| XO7           | TG         |     |   | C2            | Fp         | -   | <b>√</b> | 0.47     |      |

| XO8           | TG         |     |   | C1            | -          | p&n | <b>√</b> | 0.86     |      |

| XO9           | C2         | Fnp | - | -             | C2         | -   | p        | <b>√</b> | 0.65 |

| XO10          | TG         |     |   | C2            | -          | n   | ✓        | 0.50     |      |

Fig.7. Three-input XOR/XNOR circuits, XO4, XO7, and XO10.

#### **Conclusion:**

SCDM serves as a design methodology for three-input XOR/XNOR, which is one of the most complex and competitive as well as all-purpose three-input basic gates in arithmetic circuits. This project has favored SCDM with the wise selection of the circuit components for the PDP target. In the end, three new high performance three-input XOR/XNOR circuits with less PDP and occupied area are conceived using SCDM. The new circuits enjoy higher driving capability, transistor density, noise immunity with low-voltage operation, and the least probability to produce glitches. As a unique feature, the critical path of the presented designs consists of only two transistors, which causes low propagation delay. The area utilization for the proposed circuits enjoys improvement with the advantages of regularity and symmetry in layout.

#### **REFERENCES**

[1] C.-K. Tung, S.-H. Shieh, and C.-H. Cheng, "Low-power high-speed full adder for portable electronic applications," Electron. Lett., vol. 49, no. 17, pp. 1063–1064, Aug. 2013.

- [2] M. Aguirre-Hernandez and M. Linares-Aranda, "CMOS full-adders for energy-efficient arithmetic applications," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 19, no. 4, pp. 718–721, Apr. 2011.

- [3] M. H. Moaiyeri, R. F. Mirzaee, K. Navi, T. Nikoubin, and O. Kavehei, "Novel direct designs for 3-input XOR function for low-power and highspeed applications," Int. J. Electron., vol. 97, no. 6, pp. 647–662, 2010.

- [4] S. Goel, M. A. Elgamel, M. A. Bayoumi, and Y. Hanafy, "Design methodologies for high-performance noise-tolerant XOR-XNOR circuits," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 53, no. 4, pp. 867–878, Apr. 2006.

- [5] S. Goel, A. Kumar, and M. Bayoumi, "Design of robust, energy-efficient full adders for deep-submicrometer design using hybrid-CMOS logic style," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 14, no. 12, pp. 1309–1321, Dec. 2006.

- [6] C.-H. Chang, J. Gu, and M. Zhang, "A review of 0.18-μm full adder performances for tree structured arithmetic circuits," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 13, no. 6, pp. 686–695, Jun. 2005.

- [7] T. Nikoubin, M. Grailoo, and S. H. Mozafari, "Cell design methodology based on transmission gate for low-power high-speed balanced XOR-XNOR circuits in hybrid-CMOS logic style," J. Low Power Electron., vol. 6, no. 4, pp. 503–512, 2010.

- [8] T. Nikoubin, A. Baniasadi, F. Eslami, and K. Navi, "A new cell design methodology for balanced XOR-XNOR circuits for hybridCMOS logic," J. Low Power Electron., vol. 5, no. 4, pp. 474–483, 2009.

- [9] T. Nikoubin, M. Grailoo, and C. Li, "Cell design methodology (CDM) for balanced Carry–InverseCarry circuits in hybrid-CMOS logic style," Int. J. Electron., vol. 101, no. 10, pp. 1357–1374, 2014.

A Peer Reviewed Open Access International Journal

- [10] A. Eshra and A. El-Sayed, "An odd parity checker prototype using DNAzyme finite state machine," IEEE/ACM Trans. Comput. Biol. Bioinf., vol. 11, no. 2, pp. 316–324, Mar./Apr. 2014.

- [11] R. Roy, D. Bhattacharya, and V. Boppana, "Transistor-level optimization of digital designs with flex cells," Computer, vol. 38, no. 2, pp. 53–61, Feb. 2005.

- [12] M. Rahman, R. Afonso, H. Tennakoon, and C. Sechen, "Design automation tools and libraries for low power digital design," in Proc. IEEE Dallas Circuits Syst. Workshop (DCAS), Oct. 2010, pp. 1–4.

- [13] A. M. Shams, T. K. Darwish, and M. A. Bayoumi, "Performance analysis of low-power 1-bit CMOS full adder cells," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 10, no. 1, pp. 20–29, Feb. 2002.

- [14] J.-F. Lin, Y.-T. Hwang, M.-H. Sheu, and C.-C. Ho, "A novel high-speed and energy efficient 10-transistor full adder design," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 54, no. 5, pp. 1050–1059, May 2007.

- [15] M. Zhang, J. Gu, and C.-H. Chang, "A novel hybrid pass logic with static CMOS output drive full-adder cell," in Proc. Int. Symp. Circuits Syst. (ISCAS), vol. 5. May 2003, pp. V-317–V-320.

- [16] C.-K. Tung, Y.-C. Hung, S.-H. Shieh, and G.-S. Huang, "A low-power high-speed hybrid CMOS full adder for embedded system," in Proc. IEEE Design Diagnostics Electron. Circuits Syst. (DDECS), Apr. 2007, pp. 1–4.

- [17] T. Nikoubin, P. Bahrebar, S. Pouri, K. Navi, and V. Iravani, "Simple exact algorithm for transistor sizing of low-power high-speed arithmetic circuits," VLSI Design, vol. 2010, pp. 1–18, Jan. 2010, Art. ID 3.

- [18] C. Yang and M. Ciesielski, "BDS: A BDD-based logic optimization system," IEEE Trans. Comput.-

- Aided Design Integr. Circuits Syst., vol. 21, no. 7, pp. 866–876, Jul. 2002.

- [19] O. Kavehie, K. Navi, T. Nikoubin, and M. Rouholamini, "A novel DCVS tree reduction algorithm," in Proc. IEEE Int. Conf. Integr. Circuit Design Technol. (ICICDT), May 2006, pp. 1–7.

- [20] R. F. Mirzaee, T. Nikoubin, K. Navi, and O. Hashemipour, "Differential cascode voltage switch (DCVS) strategies by CNTFET technology for standard ternary logic," Microelectron. J., vol. 44, no. 12, pp. 1238–1250, 2013.