ISSN No: 2348-4845 International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

## Novel Modularization Approach by Presenting Architecture of a Logically Reversible Processor Based on the Von Neumann Architecture

Vineetha Vattikuti M.Tech (VLSISD), Anurag Engineering College. V.Santhosh Kumar, M.Tech Assistant Professor, Anurag Engineering College. M.Basha, M.Tech Associate Professor & HOD, Department of ECE, Anurag Engineering College.

#### **ABSTRACT:**

This business locales the reversible circuit design using novel modularization approach by displaying engineering of a legitimately reversible processor in view of the Von Neumann design that can work with low power utilization, security of force examination assault and long traverse of life because of less warmth dissemination. The association and engineering of the proposed processor is composed without any preparation. Consecutive calculations are proposed to create the parts of the reversible processor. The abilities of the new processor are resolved, the information way format is intended to handle the essential capacities, the guideline configuration is characterized and the fundamental rationale is additionally developed to control the information way. To evaluate the execution time of the calculation, we consider the computational intricacy, memory access designs and the unpredictability of the directions. Existing part outlines are contrasted and the proposed segments and hypotheses and lemmas are exhibited to demonstrate the prevalence of the proposed design. The proposed configuration is mimicked and the recreation result confirms the accuracy of the proposed plan.

#### **Index Terms:**

Reversible Logic, Reversible CPU, Quantum Cost, Garbage Output.

#### I. INTRODUCTION:

Power emergency is a fundamental issue in this day and age. As of late, the developing business sector of electronic frameworks experiences power dissemination and warmth evacuation issue. Assuming increasingly power is disseminated, framework gets to be overheated which lessens the life time of the electronic framework. The need of smaller scale electronic circuits with low power dispersal prompts the execution of reversible rationale circuit. Bennett [1] demonstrated that the coordinated mapping between the inputs and yields of reversible circuit radically decreases the force utilization and warmth dispersal of a circuit. Today security in advanced figuring and interchanges is of prime significance and in this manner cryptographic conventions assume a noteworthy part. David [2] demonstrated that reversibility assumes an indispensable part in quantum calculation. Quantum entryways and reversible rationale doors are firmly identified with each other. Like traditional reversible circuits, the quantity of info quantum bits must be equivalent to the quantity of yield quantum bits. The quantum entryways and circuits must be reversible. Along these lines, the quantum circuits can specifically be planned from reversible circuits. Processor configuration is in reality troublesome assignment and deduction а the association and engineering of the outline in reversible way requires a great deal of works. The irreversible processors scatter a lot of warmth and they require more power than the comparing reversible one. A reversible processor can defeat these issues. As reversible figuring is another period, not very many works [3], [4] in regards to reversible processor have been finished. And additionally, there is no settled patent work around there. The current reversible processor models [3], [4] need meticulousness and culmination.

These parameters inspire this work of reversible processor outline. In this work, we introduce sensible reversible processor outline engineering and calculations that attempt to top off the hole between acknowledgment of the reversible design and fulfillment of the configuration.

#### **II. BASIC DEFINITIONS**

In this segment, we display the essential definitions with respect to reversible rationale.

#### A. Reversible Gate

Reversible gate is a n-information and n-yield (signified by  $n \times n$ ) circuit that delivers a one of a kind yield design for every conceivable information design. As it were, reversible doors are circuits in which the quantity of yields is equivalent to the quantity of inputs and there is a balanced correspondence between the vector of inputs and yields.

#### **B.** Garbage Output

Undesirable or unused yield of a reversible entryway (or circuit) is known as refuse yield, i.e., the output(s) which is(are) required just to keep up the reversibility is (are) known as waste yield (s).

#### C. Quantum Cost

The quantum cost can be inferred by substituting the reversible doors of a circuit by a course of basic quantum entryways [5]. Basic quantum entryways acknowledge quantum circuits that are naturally reversible and control qubits as opposed to unadulterated rationale values. The condition of a qubit for two immaculate rationale states can be communicated as $|\psi\rangle = \alpha|0\rangle + \beta|1\rangle$ , where  $|0\rangle$  and  $|1\rangle$  signify 0 and 1, separately, and and $\alpha$  and $\beta$  are intricate numbers with the end goal that  $|\alpha|2 + |\beta|2 = 1$ . The most utilized rudimentary quantum entryways are the NOT door, the controlled-NOT (CNOT) entryway, the controlled-V door and the controlled-V+ door.

#### **III. PROPOSED WORK**

The interior game plan of a microchip differs depending on the configuration and the proposed reasons for the chip. A chip incorporates a number juggling rationale unit (ALU) and a control unit (CU) area. These two segments are associated with memory and I/O by transports which convey data and sign between the units. They have a characterized datapath. The ALU plays out the number juggling and coherent operations. The control rationale area recovers direction operation codes from memory, and starts whatever arrangement of operations of the ALU requires doing the guideline. A solitary operation code influences numerous individual datapaths, registers, and different components of the processor. Taking after strides are considered to plan the craved reversible focal preparing unit (CPU):

- 1. Outline the general structure of the reversible CPU.

- 2. Design the datapath to handle the majority of the operations of the reversible CPU.

- 3. Outline the reversible acknowledge of the flip-flops.

- 4. Outline the reversible memory circuits, (for example, cradle registers and counter circuits) utilizing the proposed reversible flip-failures of the past stride.

- 5. Plan the math circuits, for example, snake, multiplier, divider, comparator and so forth.

- 6. Plan the reversible acknowledgment of ALU.

- 7. Plan the reversible control unit of the processor by planning a proficient direction decoder.

- 8. Develop the important rationale to control the datapath.

- 9. Understand the general engineering and association of the proposed reversible processor.

- 10. Investigation of the proposed reversible focal preparing unit as far as expense and execution effectiveness.

- 11. Recreate the configuration utilizing Microwind DSCH 3.5 [6] and CMOS 45 nm Open Cell Library [7] software.

## ISSN No: 2348-4845 International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

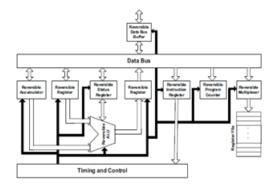

The engineering of the proposed reversible processor is appeared in Fig. 1.

#### Fig. 1. Outline of the Design of the Proposed Reversible Processor

The datapath of the proposed reversible processor is appeared in Fig. 2. The control signs are not appeared in the chart for effortlessness. As per the square outline and the datapath plan the proposed reversible processor has been separated into little parts. The reversible acknowledgment of the proposed parts is talked about in the accompanying subsections.

# Fig. 2.Datapath Design of the Proposed Reversible Processor

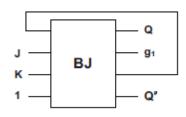

#### A. Proposed Reversible Memory Components

Flip-flops (FF) are the essential components of a register. We utilize layout coordinating calculation to propose a reversible J-K FF with least quantum cost. This J-K FF is utilized to outline the guideline register. We propose another reversible door, specifically BJ entryway [8], to plan a reversible J-K FF. The proposed reversible J-K FF requires one and only door, it creates stand out trash yield and it has 12 quantum cost. The outline of the proposed J-K FF is appeared in Fig. 3. The proposed reversible J-K FF accomplishes the change of 66.6% as far as number of entryways, 66.6% as far as rubbish yields, 66.6% as far as deferral and 4.28% as far as quantum expense over the current best one [9].

#### Fig. 3.Proposed Reversible J-K Flip-Flop

This proposed J-K FF is utilized to plan the registers. A reversible 16-bit register can be planned utilizing sixteen HNFG entryways and sixteen proposed J-K FFs. The J-K FFs take the inputs through HNFG doors and with the change of the clock beat they deliver the ordinary and supplemented yields. The arrangement counter is additionally planned utilizing four proposed J-K FFs and four Feynman doors. The J-K FFs change states with the positive clock edge and the counter tallies from 0 to 15. This upgraded outline of succession counter delivers 4 trash yields.

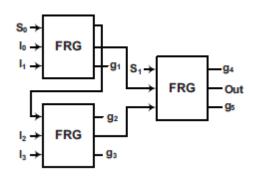

#### **B.** Proposed Reversible Multiplexer

Reversible Multiplexer (Mux) is required to choose a specific contribution from different info sources. A reversible 4-to-1 mux is outlined with Fredkin entryways. The proposed outline of 4-to-1 mux is appeared in Fig. 4. The proposed reversible 4-to-1 mux accomplishes the change of 57.14% regarding number of entryways, 54.54% as far as trash yields, 73.68% as far as quantum expense and 57.14% as far as postponement over the current best one [10].

Fig. 4.Proposed Reversible 4-to-1 Multiplexer

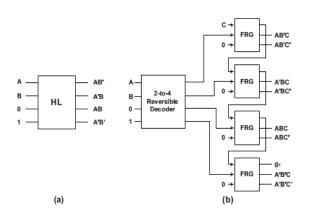

#### C. Proposed Reversible Decoder

The control unit obliges decoders to interpret the guidelines. We propose the configuration of a n-to-2n decoder. To design his decoder at first we propose a reversible 2-to-4 decoder which was utilized to build a 3-to-8 decoder et cetera. The outline of an enhanced 2to-4 decoder was extremely testing as a current 2-to-4 decoder [11] requires stand out door and it doesn't create any rubbish yields. Thus, there was no extension to enhance door tally, trash yields and defer. Thorough hunt was utilized to locate the reversible door with ideal arrangement which creates the base quantum cost. We propose another reversible door, in particular HL entryway [8] to outline a 2-to-4 decoder. The proposed 2-to-4 decoder requires stand out entryway with no refuse yield which has 7 quantum cost. Our proposed outline has the same door check, refuse yields and defer. Yet, it has enhanced quantum cost. A reversible 3-to-8 decoder can be composed utilizing one 2-to-4 reversible decoder and four Fredkin entryways. The accomplishment of the configuration of 3-to-8 outline was more noteworthy as the current best 3-to-8 decoder [12] is very little upgraded. The outlines of the proposed reversible 2-to-4 decoder and 3-to-8 decoder are appeared in Fig. 5(a) and Fig. 5(b) separately.

Fig. 5.Proposed Reversible (a) 2-to-4 Decoder (b) 3-to-8 Decoder

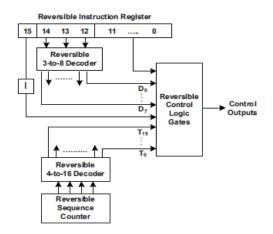

#### **D. Proposed Reversible Control Unit**

A control unit is a circuit that coordinates operations inside the PC's processor by coordinating the information and yield of a PC framework. The control unit comprises of two decoders, a grouping counter, and various control rationale entryways. It brings the guideline from direction register. The inputs to the control rationale doors originate from two decoders, flip-lemon and guideline register.

Fig. 6.Proposed Reversible Control Unit

The yields of the control rationale circuit are: signs to control the inputs of the registers, signs to control the read and compose inputs of memory and signs to set, clear or supplement the flip-flops.A regulated configuration system has been proposed to outline the control unit which associates all the proposed parts with some other additional hardware. The piece graph of the proposed control unit is appeared in Fig. 6.

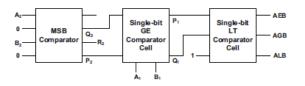

#### E. Proposed Reversible Comparator

A size comparator takes two numbers as contribution to parallel shape and figures out if one number is more noteworthy than, not exactly or equivalent to the next number. Comparators are utilized as a part of focal handling unit. We propose a minimized and enhanced calculation for developing a conservative reversible nbit paired comparator circuit. With a specific end goal to enhance the configuration, we utilize quantum cost minimization calculation to outline a n-bit comparator.

Diminishment tenets and calculations are connected by layout coordinating to minimize the quantum cost. The entire comparator is partitioned into three modules. They are as per the following: We propose a MSB comparator circuit for looking at the nth piece (MSB) of two n-bit numbers. At that point, a solitary piece GE (more prominent or equivalent) comparator cell has been intended to create more noteworthy and equivalent sign for the rest of the (n-1) bits of two numbers with the past correlation aftereffect of MSB. A solitary piece LT (not exactly) comparator cell is intended to decide the not as much as sign. These three parts with least quantum expense are then fell with each other utilizing productive systems to plan 2-bit and n-bit reversible paired comparators all the more minimalistic ally. A reversible 2-bit double comparator comprises of a proposed reversible MSB comparator, a solitary piece GE comparator and a solitary piece LT comparator circuit. The reversible outline of 2-bit parallel comparator is appeared in Fig. 7. The point of interest configuration of the individual pieces is not appeared here because of space imperatives.

#### Fig. 7. Proposed Reversible 2-bit comparator

The proposed reversible 64-bit comparator accomplishes the change of 24.4% as far as number of entryways, 19.9% in terms of refuse yields, 7.7% regarding quantum cost, 25.77% as far as range and 3.43% as far as control over the current best one [13].

#### F. Proposed Reversible Multiplier

Multiplier circuit is utilized as a part of a processor. Multiplier circuit chiefly has two segments: Partial Product Generation (PPG) circuit and the Multi-Operand Addition (MOA) circuit. A multiplier circuit can be advanced in two ways. The calculation of the increase can be enhanced, and also, the development method of the PPG circuit and MOA circuit can be improved. Firstly, we build proficient layout utilizing reversible doors to diminish the quantum cost and defer. Also, we utilize a productive looking system to locate the proper positions of various segments of the proposed circuit. At last, we propose two effective calculations which create fast least cost PPG circuit and MOA circuit of the proposed multiplier. The near study demonstrates proposed reversible that the  $4 \times 4$ multiplier accomplishes the change of 26.32% as far as number of doors, 12.5% as far as junk yields, 17% as far as quantum expense and 20.97% as far as steady inputs over the current best one [14]. The proposed reversible  $n \times n$  multiplier requires n(2n - 1) gates, 4n(n - 1) +1garbage outputs and 17n(n-1)+1 quantum cost; where as the best existing fault tolerant reversible multiplier [14] requires n(2n - 1) + 5n/2 gates, 2n(n - 1)1) garbage outputs and n(19n - 17) + 7 + 2 n/2quantumcost.

#### G. Proposed Reversible Divider

Divider circuit is utilized as a part of a processor. We propose two design methods to build reversible n-bit drifting point non-reestablishing division circuit. In the primary methodology of the reversible divider circuit, we propose convey proliferate 2's supplement viper and shifters. To accelerate the division procedure, we propose a noteworthy change in the second approach of the reversible divider. We discard the convey spread to dodge the proliferation postpone and present two new vectors and a solitary convey look-ahead snake circuit. Subtraction is executed utilizing 2's supplement snake. Both of the methodologies can deal with drifting point numbers. Thorough pursuit strategy is utilized to locate the proper positions of reversible entryways to get the base cost parameters for a particular capacity that are utilized to plan the reversible divider circuit all the more minimalistically. The relative study demonstrates that the proposed reversible customary 4-bit divider accomplishes the change of 62.92% regarding number of entryways, 70.97% as far as junk yields and 74.83% as far as quantum expense over the current best one [15].

## ISSN No: 2348-4845 International Journal & Magazine of Engineering, Technology, Management and Research

A Peer Reviewed Open Access International Journal

The proposed reversible fast 4-bit divider accomplishes the change of 22.47% as far as number of doors, 17.74% as far as waste yields and 43.87% regarding quantum cost over the current best one [15].

#### **IV. CONCLUSIONS**

In this work, reversible rationale combinations with the base cost elements are completed for the segments of the reversible processor. Numerous essential commitments have been made in the writing towards the reversible usage of number juggling and intelligent structures; be that as it may, there have not been numerous endeavors coordinated towards productive methodologies for outlining reversible ALU (Arithmetic Logic Unit). At present we are taking a shot at the outline of the reversible ALU. We will propose a proficient way to deal with configuration the reversible ALU. At last every one of the segments of the reversible CPU (Central Processing Unit) will be interfaced together with essential associating circuits to get the complete reversible CPU. The proposed reversible CPU can make a huge commitment in the field of low power reversible figuring and quantum registering.

#### ACKNOWLEDGMENT

This work was done under the help of Prime Minister's Research and Higher Studies Fund given by the Prime Minister's Office and ICT Innovation Fund given by the Ministry of ICT, Government of the People's Republic of Bangladesh.

#### REFERENCES

[1]C. H. Bennett, "Logical reversibility of computation," IBM J. Researchand Development, vol. 17, pp. 525–532, 1973.

[2]D. P. DiVincenzo, "Quantum gates and circuits," Proceedings of theRoyal Society of London A: Mathematical, Physical and Engineering Sciences, vol. 454, no. 1969, pp. 261–276, 1998.

[3]H. Axelsen, R. Glck, and T. Yokoyama, "Reversible machine code and its abstract processor

architecture," in Computer Science Theory andApplications, ser. Lecture Notes in Computer Science. Springer BerlinHeidelberg, 2007, vol. 4649, pp. 56–69.

[4]M. Thomsen, H. Axelsen, and R. Glck, "A reversible processor archi-tecture and its reversible logic design," in Reversible Computation, ser. Lecture Notes in Computer Science. Springer Berlin Heidelberg, 2012, vol. 7165, pp. 30–42.

[5]M. Nielsen and I. Chuang, Quantum Computation and Quantum Infor-mation. Cambridge Univ. Press, 2000.

[6]Microwinddsch - schematic editor and digital simulator. [Online]. Available:

http://www.microwind.net/dsch.ph

[7]Cmos 45 nm open cell library. [Online]. Available: http://www.si2.org/openeda.si2.org/projects/nangatelib

[8]L. Jamal, M. M. Alam, and H. M. H. Babu, "An efficient approach to design a reversible control unit of a processor," Sustainable Computing:Informatics and Systems, vol. 3, no. 4, pp. 286 – 294, 2013.

[9]A. S. M. Sayem and M. Ueda, "Optimization of reversible sequential circuits," Journal of Computing, vol. 2, no. 6, pp. 208 – 214, 2010.

[10]M. Polash and S. Sultana, "Design of a lut-based reversible field programmable gate array," Journal of computing, vol. 2, no. 10, pp. 103–108, 2010.

[11]M. Nachtigal and N. Ranganathan, "Design and analysis of a novel reversible encoder/decoder," in Nanotechnology (IEEE-NANO), 201111th IEEE Conference on, Aug 2011, pp. 1543–1546.

[12]M. Shamsujjoha and H. Babu, "A low power fault tolerant reversible decoder using mos transistors," in VLSI Design and 2013 12th In-ternational Conference on Embedded Systems (VLSID), 2013 26th International Conference on, Jan 2013, pp. 368–373.

[13]C. Vudadha, P. Phaneendra, V. Sreehari, S. Ahmed, N. Muthukrishnan, and M. Srinivas, "Design

of prefix-based optimal reversible comparator," in VLSI (ISVLSI), 2012 IEEE Computer Society Annual Symposium on, Aug 2012, pp. 201–206.

[14]X. Qi, F. Chen, K. Zuo, L. Guo, and Y. L. M. Hu, "Design of fast fault tolerant reversible signed multiplier," International Journal of PhysicalSciences, vol. 7(17), pp. 2506–2514, 2012.

[15]N. Nayeem, A. Hossain, M. Haque, L. Jamal, and H. Babu, "Novel reversible division hardware," in Circuits and Systems, 2009. MWSCAS'09. 52nd IEEE International Midwest Symposium on, 2009, pp. 1134– 1138.